# Modular Equalization System Using Dual Phase-Shift-Controlled Capacitively-Isolated Dual Active Bridge Converters to Equalize Cells and Modules in Series-Connected Lithium-Ion Batteries

Masatoshi Uno, Member, IEEE, and Koji Yoshino

Abstract—Conventional lithium-ion battery (LIB) packs comprising series-connected modules need cell and module equalizers separately, resulting in increased system complexity. This paper proposes a modular equalization system using dual phase-shift (DPS)-controlled capacitively-isolated dual active bridge (CIDAB) converters. Each module contains an intra-module CIDAB converter that performs direct cell-to-cell equalization. Meanwhile, switching legs of adjacent modules' CIDAB converters are connected through an LC tank to configure an inter-module CIDAB converter that equalizes module voltages. The switching legs of CIDAB converters are utilized for both the intra- and inter-module equalizers, achieving the simplified system. Based on the proposed DPS control, the PS angles of both the intra- and inter-module CIDAB converters are manipulated to perform cell and module equalization. The prototype of the proposed modular equalization system for two LIB modules, each consisting of twelve cells was built and tested. Cells and module voltages in the proposed system were sufficiently equalized, demonstrating the efficacy of the proposed equalization system.

Keywords—Capacitive isolation, dual active bridge converter, equalization, lithium-ion battery, voltage imbalance.

#### I. INTRODUCTION

# A. Cell Imbalance and Equalizers for Lithium-Ion Batteries

Lithium-ion battery (LIB) cells are connected in series to form a pack or module to meet the voltage requirement of loads. Individual cell voltages gradually become imbalanced due to characteristic mismatches, such as capacity, internal impedance, self-discharge rate, coulombic efficiency, and ambient temperatures [1], [2]. In voltage-imbalanced LIB modules, some cells with high or low voltages might be over-charged or discharged beyond safety boundaries specified by manufacturers. Charging and discharging LIB cells beyond

M. Uno and K. Yoshino are with the Graduate School of Science and Engineering, Ibaraki University, Hitachi 316-8511, Japan (e-mail: masatoshi.uno.ee@vc.ibaraki.ac.jp).

safety boundaries may trigger premature irreversible degradation or hazardous consequences, such as fire or, in the worst case, an explosion.

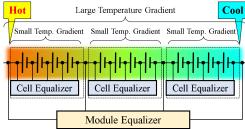

In large-scale LIB packs, such as electric vehicles, a modular structure is mainstream. Several to dozen cells are connected in series to form a module, and then multiple modules are connected in series to form a large pack or string, as illustrated in Fig. 1. In such large-scale systems, in addition to cell voltage imbalance in each module, module voltage imbalance is also very likely due to uneven temperature distribution. Cell temperatures in each module are relatively even because of the small geometry of modules. Module temperatures, on the other hand, are prone to be uneven due to their large geometry. In general, the uneven temperature distribution is cited as a top concern that accelerates voltage imbalance as well as premature degradation [2]–[4]. To operate LIB systems safely for years, cell and module voltage equalizations are indispensable to mitigate or even eliminate such voltage imbalance.

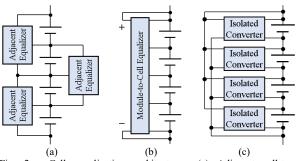

Various kinds of voltage equalizers, also known as balancers, have been proposed for series-connected LIBs. Several kinds of equalization architectures, such as adjacent cell-to-cell architectures using nonisolated bidirectional converters [Fig. 2(a)], such as PWM converters [5]–[7] and switched capacitor converters [8]–[13], module-to-cell architectures using single-input—multi-output converters [Fig. 2(b)] [14]–[26], module-to-cell architecture using isolated converters [Fig. 2(c)] [27], etc., have been proposed. These architectures and circuit topologies are relatively simple. However, since the numbers of passive components, such as inductors, capacitors, and transformers, are proportional to the cell count n, these equalizers are prone to be bulky as n increases.

Fig. 1. Modular battery structure and its uneven temperature distribution.

## > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

Fig. 2. Cell equalization architectures. (a) Adjacent cell-to-cell architecture with nonisolated bidirectional converters. (b) Module-to-cell architecture with single-input—multi-output converter. (c) Module-to-cell architecture with isolated converters.

## B. Cell Equalizers with Selection Switches

Among conventional equalization architectures is the direct cell-to-cell or module-to-cell architecture using selection switches, as shown in Fig. 3. Although numerous selection switches are necessary, the passive component count can be considerably reduced in comparison with other equalization architectures. The reduced passive component count is an attractive feature from the viewpoint of circuit volume because passive components (especially magnetic components) are rather bulkier than semiconductor devices.

Representative cell equalizers with selection switches are shown in Fig. 3. Selection switches in these topologies are a bidirectional switch consisting of two MOSFETs connected back-to-back to block bidirectional current flow. The most charged cell (or the least charged cell) in a module is selected as a target cell by the selection switches to connect a converter. In the module-to-cell architecture [Fig. 3(a)], an isolated converter transfers energy between a target cell and module [28]-[31]. With polarity switches, as shown in Fig. 3(b), the selection switch count can be reduced as low as n + 5 [32]. However, since the energy transfer in the module-to-cell architectures is limited between the module and a target cell, some cells in a module are unnecessarily charged and discharged in the course of equalization, resulting in a slowed equalization process and reduced overall efficiency. Furthermore, in addition to the necessity of a bulky transformer, isolated converters in these module-to-cell equalization architectures must be rated for the full module voltage as it is directly connected to the module.

The direct cell-to-cell architecture using a unidirectional converter [see Fig. 3(c)] can directly transfer energy between target cells [33], [34], but the increased selection switch count (4n) is a major drawback. The direct cell-to-cell architecture with an energy storage medium [Fig. 3(d)], such as a capacitor, inductor, and resonant tank, can reduce the selection switch count as low as n + 1 [35]–[40]. However, since selection switches in many existing topologies have to operate at a high frequency in conjunction with four unidirectional switches  $(Q_{aH}, Q_{aL}, Q_{bH}, \text{ and } Q_{bL})$ , numerous high-frequency gate drivers are necessary, increasing the system cost and complexity—selection switches in other architectures can operate at a low frequency, and high-frequency gate drivers are not necessary.

Fig. 3. Equalization architectures with selection switches. (a) Module-to-cell architecture. (b) Module-to-cell architecture with polarity switches. (c) Direct cell-to-cell architecture with unidirectional converter. (d) Direct cell-to-cell architecture with energy storage medium.

Although equalizers with selection switches achieve miniaturized circuit thanks to the reduced passive component counts, voltage stresses of selection switches are prone to soar as the number of cells in a string increases. Switches at the furthest ends of the string, for example, are exposed to a full string voltage.

# C. Conventional Modular Equalization Systems

Multi-layer or modular equalization systems (hereafter referred to as modular systems) have been proposed for largescale systems to realize good modularity (or scalability) and fast equalization performance [41]-[48], as illustrated in Fig. 1. In such systems, LIB cells in each module are equalized by celllevel equalizers, and module equalizers unify module voltages. The design of cell-level equalizers and the number of cells in each module are fixed and unchanged, while the system can be flexibly scaled up by adding modules and module-level equalizers. Any kinds of equalizers can be employed as celland module-level equalizers. Conventional modular systems [42], [48] simply employ cell- and module-level equalizers separately, hence increasing the system complexity and cost. Equalization systems in [43], [45], [47] can reduce the number of module-level equalizers by using a multi-winding transformer-based converter, but the existence of the multiwinding transformer is often cited as a major concern that increases the design difficulty and impairs the modularity [49].

## D. Research Objective

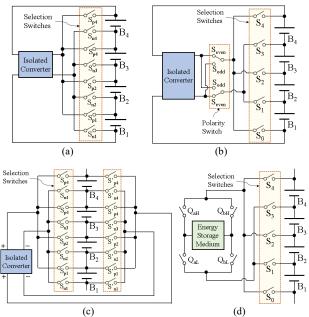

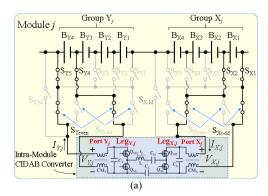

This paper proposes a novel modular equalization system based on equalizers with selection switches. A direct-cell-tocell equalizer with selection switches using a capacitivelyisolated dual-active bridge (CIDAB) converter is employed as

## > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

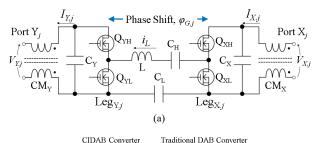

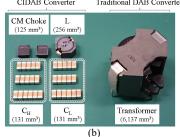

Fig. 4. (a) Half-bridge CIDAB converter. (b) Key passive components necessary in CIDAB converter and traditional transformer-based DAB converter.

an intra-module equalizer. Meanwhile, by adding an LC tank between adjacent switching legs of adjacent modules' CIDAB converters, a CIDAB-based inter-module equalizer is configured without adding active switches. With the proposed dual phase-shift (DPS) control technique, PS angles of not only the intra-module CIDAB converter but also the inter-module CIDAB converter are manipulated to perform cell and module equalization.

The rest of this paper is organized as follows. Section II presents the proposed modular equalization system and its major features. Section III discusses operation principles of the cell equalization mode and module equalization mode, separately, followed by the equalization algorithms in Section IV. Section V discusses a design example of the CIDAB

converter for LIB modules consisting of twelve cells connected in series. The experimental results of the proposed modular equalization system for two modules will be presented in Section VI. The proposed and conventional equalizers will be compared from the viewpoint of component counts and reported efficiency in Section VII.

#### II. PROPOSED MODULAR EQUALIZATION SYSTEM

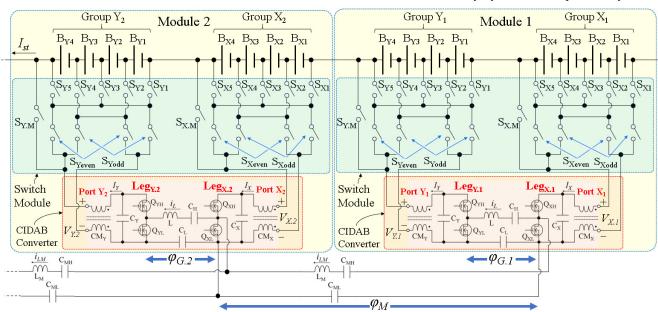

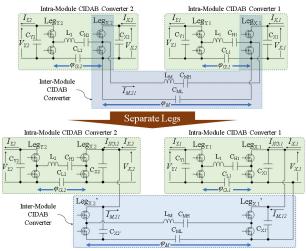

The proposed modular equalization system consists of series-connected LIB modules, each comprising two groups of series-connected cells, CIDAB converter, and switch module. This section explains the CIDAB converter and switch modules, which are the key components of the proposed system, followed by the system configuration.

# A. Capacitively-Isolated Dual Active Bridge Converter

An isolated converter is indispensable to transfer energy between cells at different voltage levels. Isolated converters, such as flyback converters and DAB converters, are generally employed in conventional battery cell equalization systems, but each isolated converter requires a bulky lossy transformer. In the proposed equalization system, instead of traditional transformer-based isolated converters, CIDAB converters are employed to achieve reduced circuit volume. Energy densities of discrete capacitors are reportedly in the range of more than three orders of magnitude over that of similarly scaled magnetic components [50], [51]. Previous studies reported the reduced circuit volume of the resonant converters thanks to the capacitive isolation [52], [53].

The half-bridge CIDAB converter is shown in Fig. 4(a). Two switching legs ( $Leg_{X,j}$  and  $Leg_{Y,j}$ ) are isolated by capacitors  $C_H$  and  $C_L$ , instead of a transformer. The fundamental operation principle of the CIDAB converter is very similar to that of conventional DAB converters. The high- and low-side switches are driven with 50% duty cycle in a complementary manner

Fig. 5. Proposed modular equalization system using selection switches and capacitively-isolated DAB converter.

while the phase shift angle  $\varphi_{G,j}$  between  $\text{Leg}_{X,j}$  and  $\text{Leg}_{Y,j}$  is manipulated to adjust the magnitude and direction of power transfer between Port  $X_j$  and  $Y_j$ . Switches in the CIDAB converter can be turned-on and -off at zero voltage switching (ZVS), similar to conventional DAB converters. Although common-mode (CM) chokes are necessary to suppress common-mode currents, these can be tiny in comparison with an isolation transformer.

Figure 4(b) exemplifies the comparison of key passive components necessary in the CIDAB converter and conventional half-bridge DAB converter for the same power rating of 50 W—switches and smoothing capacitors (C<sub>X</sub> and C<sub>Y</sub>), which are common to both converters, are excluded. Although the number of passive components necessary increases, the passive component volume would be reduced by 90%.

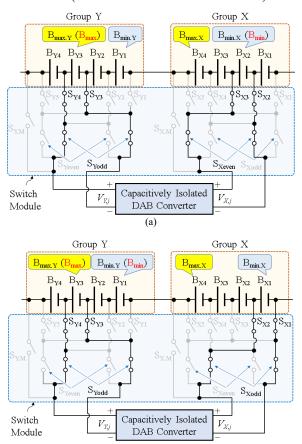

## B. Switch Module

The switch module, which selects target cells depending on voltage imbalance conditions, consists of selection switches ( $S_{Xi}$  and  $S_{Yi}$ , where i = 1...4) and polarity switches ( $S_{Xodd}$ ,  $S_{Xeven}$ ,  $S_{Yodd}$ , and  $S_{Yeven}$ ), as shown in Fig. 5. Each switch comprises two N-channel MOSFETs connected back-to-back, and each module contains n + 12 switches (n is the cell count in each module).

The selection switches literally select target cells or a whole group while polarity switches match the voltage polarities of the target cells and CIDAB converter. For example, to select the odd-numbered cell of  $B_{X1}$ , the selection switches of  $S_{X1}$  and  $S_{X2}$  and the polarity switch of  $S_{Xodd}$  are turned on. To select the even-numbered cell of  $B_{X2}$ , on the other hand, the selection switches of  $S_{X2}$  and  $S_{X3}$  and the polarity switch of  $S_{Xeven}$  are turned on.

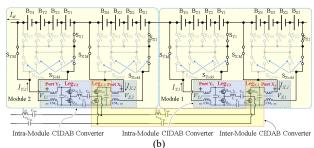

# C. System Configuration

The proposed modular equalization system for two LIB modules, each consisting of eight cells connected in series are illustrated in Fig. 5. Each module contains a switch module and an intra-module CIDAB converter that performs cell equalization. Series-connected cells in each module are subdivided into two groups of Group  $X_j$  and  $Y_j$  (j = 1, 2, ..., m, where m is the number of modules), and are connected to Port  $X_j$  and  $Y_j$  of the CIDAB converter.

Each CIDAB converter contains two switching legs of  $Leg_{X,j}$  and  $Leg_{Y,j}$ . An LC tank consisting of  $C_{MH}$ ,  $C_{ML}$ , and  $L_{M}$  is added between adjacent  $Leg_{X}$ 's to configure an inter-module CIDAB converter that performs module equalization. No additional switches are necessary for the inter-module equalizer because  $Leg_{X,j}$  is utilized for both the intra- and inter-module CIDAB converters.

To perform cell and module equalizations, two control freedoms are necessary. A dual PS (DPS) control technique is also proposed for the modular equalization system. The DPS control technique manipulates not only the PS angel  $\varphi_{G,j}$  of each intra-module CIDAB converter to equalize cell voltages (or group voltages) but also the PS angel  $\varphi_M$  between adjacent

Leg<sub>X</sub>'s (i.e., the PS angle of the inter-module CIDAB converter) to balance module voltages.

#### D. Features

The most prominent feature is that the inter-module CIDAB converter can be configured by simply adding an LC tank between adjacent modules. Since no additional active switches are necessary, the number of switching legs as well as gate driver circuits can be reduced in comparison with conventional systems, hence contributing to the simplified circuit. The reduced circuit volume of the converter thanks to the capacitive isolation is also a benefit.

The proposed equalization system is fully modular and offers good modularity or scalability. The number of cells in each module and module design are fixed, while the number of modules can flexibly be changed to meet system requirements. The number of modules can be arbitrarily extended by simply adding LC tanks without redesigning the modules nor adding active switches.

The major drawback of the proposed system is that switching in each module should occur synchronously for the intermodule CIDAB converters to properly operate. In other words, the proposed modular equalization architecture should be a centralized system, not distributed one, posing wiring and communication issues. The development of distributed modular equalization systems will be of primary importance in our future works.

#### III. EQUALIZATION MODE

The proposed modular equalization system operates either in the cell equalization mode or module equalization mode. The cell and module equalization modes do not coincide. Although cells and modules cannot be equalized simultaneously,

Fig. 6. Equalization modes. (a) Cell equalization mode. (b) Module equalization mode.

equalizing cells and modules separately slowly would be satisfactory. As long as batteries are properly designed and manufactured, the mismatch in voltage or state-of-charge grows very slowly in practical use. Previous works reported that an equalization current equivalent to one-hundredth of charging or discharging current is sufficient to preclude voltage imbalance [54], [55].

Images of the cell and module equalization modes are illustrated in Figs. 6(a) and (b), respectively.

# A. Cell Equalization Mode

Target cells (the least charged cell and the most charged cell) in each module are selected by the switch module so that the intra-module CIDAB converter directly transfers power from the most charged cell in a group to the least charged cell in another group. The magnitude and direction of power transfer in the *j*-th module (j = 1, 2, ..., m) are adjusted by the PS angle  $\varphi_{Gj}$  between Leg<sub>X,j</sub> and Leg<sub>Y,j</sub>. Meanwhile, the PS angle  $\varphi_M$  between adjacent modules' CIDAB converters is set to be zero so that the module equalization does not take place.

The input and output currents (or  $I_{X_j}$  and  $I_{Y_j}$ ) of the intramodule CIDAB converter in the cell equalization mode are given by

$$\begin{cases} I_{X.j} = \frac{V_{Ycell.j}}{2f_s L} d_{\varphi G.j} | 0.5 - d_{\varphi G.j} | \\ I_{Y.j} = \frac{V_{Xcell.j}}{2f_s L} d_{\varphi G.j} | 0.5 - d_{\varphi G.j} | \end{cases}$$

(1)

where  $f_s$  is the switching frequency, L is the inductance, and  $V_{Xcell,j}$  and  $V_{Ycell,j}$  are the voltages of cells connected to Port  $X_j$  and  $Y_j$ .  $d_{\phi G,j}$  is the PS duty cycle of the intra-module CADAB converter defined as

$$d_{\varphi G.j} = \frac{\varphi_{G.j}}{2\pi} \tag{2}$$

# B. Module Equalization Mode

Whole groups are selected by  $S_{X.M}$ ,  $S_{X.M}$ ,  $S_{Y.M}$ , and  $S_{Y.M}$  of the switch module, and the inter-module CIDAB converter

Fig. 7. Equivalent circuit of intra- and inter-module CIDAB converters in module equalization mode.

transfers power between adjacent Group X's. The PS angle  $\varphi_M$  between adjacent Legx's is manipulated to determine the magnitude and direction of power transfer between adjacent Group X's. However, since the inter-module CIDAB converter is configured between adjacent Group X's, voltage imbalance between Groups  $X_j$  and  $Y_j$  occurs to some extent. To balance the group voltages,  $\varphi_{G,j}$  should also be manipulated at the same time. Thus, the module equalization mode simultaneously manipulates  $\varphi_{G,j}$  and  $\varphi_M$  (i.e., the DPS control) so that the intramodule CIDAB converter transfers power between Groups  $X_j$  and  $Y_j$  in each module.

Leg<sub>X,j</sub> is shared by both the intra- and inter-module CIDAB converters, which complicates the analysis of the module equalization mode. To simplify the analysis, the shared Leg<sub>X,j</sub> can be equivalently separated. The equivalent circuit of the intra- and inter-module CIDAB converters is shown in Fig. 7, in which the intra- and inter-module CIDAB converters have separate switching legs of Leg<sub>X,j</sub> and Leg<sub>X,j</sub>. This figure suggests that the port current of  $I_{X,j}$  contains not only the group equalization current by the intra-module CIDAB converter ( $I_{XG,j}$ ) but also the module equalization current due to the intermodule CIDAB converter ( $I_{M,j(j+1)}$ ) and  $I_{M,(j+1)j}$ ). Meanwhile, the port current of  $I_{Y,j}$  is equal to the group equalization current of  $I_{YG,j}$ .

The input and output currents ( $I_{XG,j}$  and  $I_{YG,j}$ ) of the intramodule CIDAB converter due to the group equalization is expressed as

$$\begin{cases}

I_{XG.j} = \frac{V_{YG.j}}{2f_sL} d_{\varphi G.j} | 0.5 - d_{\varphi G.j}| \\

I_{YG.j} = \frac{V_{XG.j}}{2f_sL} d_{\varphi G.j} | 0.5 - d_{\varphi G.j}|

\end{cases}$$

(3)

where  $V_{XG,j}$  and  $V_{YG,j}$  are the voltage of Group X and Y in the *j*-th module.

Similarly, the input and output currents ( $I_{M,j(j+1)}$ ) and  $I_{M,(j+1)j}$ ) of the inter-module CIDAB converter due to the module equalization is expressed as

$$\begin{cases} I_{M,j(j+1)} = \frac{V_{XG,(j+1)}}{2f_{S}L_{M}} d_{\varphi M} |0.5 - d_{\varphi M}| \\ I_{M,(j+1)j} = \frac{V_{XG,j}}{2f_{S}L_{M}} d_{\varphi M} |0.5 - d_{\varphi M}| \end{cases}$$

(4)

where  $d_{\phi M}$  is the PS duty cycle of the inter-module CIDAB converter defined as

$$d_{\varphi M} = \frac{\varphi_M}{2\pi} \tag{5}$$

## IV. EQUALIZATION ALGORITHM

As explained in the previous sections, the proposed modular equalization system operates either in the cell equalization mode or module equalization mode, and these two equalization modes do not coincide. The cell and module equalization modes are performed independently with separate algorithms.

#### A. Cell Equalization Mode

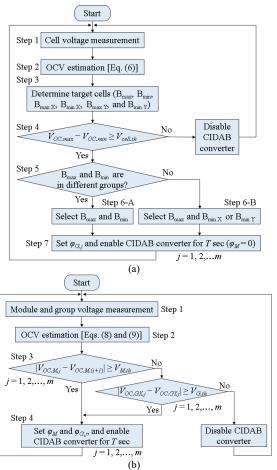

The flowchart of the cell equalization algorithm is shown in Fig. 8(a). Firstly, all cell voltages are measured in Step 1 to

Fig. 8. Equalization algorithms in (a) cell equalization mode and (b) module equalization mode.

estimate open-circuit voltages (OCVs) of cells. A voltage drop due to an internal impedance of a cell needs to be compensated based on a non-linear impedance model to accurately estimate OCVs [56], [57]. However, to simplify the OCV estimation, cells can be equivalently treated as a series connection of a voltage source and an internal resistance. Step 2 employs the following equation to estimate the OCV of the *i*-th cell in each module,

$$V_{OC.i} = V_{cell.i} + r(I_{eq} + I_{st})$$

$$\tag{6}$$

where  $V_{cell,i}$  is the voltage of the *i*-th cell in a module, r is the internal resistance, and  $I_{st}$  is the string current.  $I_{eq}$  is the equalization current supplied to/from the intra-module CIDAB converter.

$$I_{eq} = \begin{cases} I_{X,j} \\ -I_{Y,j} \\ 0 \end{cases} \tag{7}$$

$I_{Xj}$  and  $I_{Yj}$  in the cell equalization mode are given by (1).

Based on the estimated OCVs, target cells that will be selected by the switch module are determined in Step 3. The target cells include the most charged cell and the least charged cell in the module ( $B_{max}$  and  $B_{min}$ ), and the most charged cells and the least charged cells in Group  $X_i$  and  $Y_i$  ( $B_{max.Y}$ ,  $B_{max.Y}$ ,

Fig. 9. Examples of (a) Step 6-A and (b) Step 6-B in cell equalization mode.

$B_{min.X}$ , and  $B_{min.Y}$ ).

Step 4 judges whether cells are balanced. If the largest OCV difference among cells in a module exceeds a threshold voltage level, the cell equalization starts. The difference between OCVs of  $B_{max}$  and  $B_{min}$  (i.e.,  $V_{OC.max} - V_{OC.min}$ ) is calculated and compared with the threshold voltage of  $V_{cell.th}$ . If  $V_{OC.max} - V_{OC.min} < V_{cell.th}$ , the intra-module CIDAB converter is disabled to stop cell equalization. If  $V_{OC.max} - V_{OC.min} \ge V_{cell.th}$ , the operation moves toward cell equalization by manipulating the switch module and activating the CIDAB converter.

The equalization process differs depending on whether  $B_{max}$  and  $B_{min}$  exist in different groups because the intra-module CIDAB converter cannot transfer power between cells in the same group. Step 5 judges whether  $B_{max}$  and  $B_{min}$  exist in the same group. If  $B_{max}$  and  $B_{min}$  exist in different groups (e.g.,  $B_{max}$  in Group  $X_j$  and  $B_{min}$  in Group  $Y_j$ ), the operation moves to Step 6-A so that the switch module selects  $B_{max}$  and  $B_{min}$  as the target cells. On the other hand, if  $B_{max}$  and  $B_{min}$  exist in the same group, the operation moves to Step 6-B, in which the switch module selects  $B_{max}$  and either  $B_{min.X}$  or  $B_{min.Y}$  that does not exist in the same group as  $B_{max}$ .

Examples of Steps 6-A and 6-B for a module consisting of eight cells are illustrated in Fig. 9. In the example case of Step 6-A in Fig. 9(a),  $B_{Y3}$  and  $B_{X2}$  are the most and the least charged

cells, respectively.  $B_{X4}$  is the most charged cell in Group X, and  $B_{Y1}$  is the least charged cell in Group Y. Since  $B_{Y3}$  ( $B_{max}$ ) and  $B_{X2}$  ( $B_{min}$ ) exist in different groups, these cells are selected as the target cells. In the example case of Step 6-B in Fig. 9(b),  $B_{Y3}$  and  $B_{Y1}$  are the most and the least charged cells in the module, respectively, while  $B_{X4}$  and  $B_{X1}$  are the most and the least charged cells in Group X. In this case,  $B_{Y3}$  is selected as the target cell of  $B_{max}$  to supply energy.  $B_{Y1}$  is the least charge cell ( $B_{min}$ ) in the module, but it cannot be selected because it exists in the same group. Instead, the least charged cell in the other group ( $B_{X1}$ ) is selected as the target cell to receive energy.

Once the target cells are determined and selected, the intramodule CIDAB converter is enabled with setting  $\varphi_{G,j}$  properly in Step 7. Meanwhile,  $\varphi_M$  should be zero so that no power transfer between modules occurs. The series of steps in Fig. 8(a) is performed for all modules and is repeated every T sec as long as  $V_{OC.max} - V_{OC.min}$  is greater than  $V_{cell.th}$ . If  $V_{OC.max} - V_{OC.min}$ becomes lower than  $V_{cell.th}$ , cells are judged to be equalized well, and the CIDAB converter is disabled.

#### B. Module Equalization Mode

Contrary to the cell equalization mode, the module equalization algorithm does not need to detect targets because whole groups and modules are selected to exchange power, as illustrated in Fig. 6(b).

The flowchart of the module equalization is shown in Fig. 8(b). The module and group voltages are measured in Step 1 to estimate OCVs. As mentioned in Section III-B, the input and output currents of the CIDAB converter (i.e.,  $I_{X,j}$  and  $I_{Y,j}$ ) contain not only the current due to the group equalization ( $I_{GX,j}$  and  $I_{GY,j}$ ) but also the current due to the module equalization ( $I_{M,j(j+1)}$ ) and  $I_{M,(j+1)j}$ ), as expressed by (3) and (4). Hence, OCVs of groups and modules should be estimated by compensating the voltage drops due to both the group equalization and module equalization.

Similar to the simple model used for the cell OCV estimation, the OCVs of group  $X_j$  and  $Y_j$  in the *j*-th module,  $V_{OC,GX_j}$ , and  $V_{OC,GY_j}$ , are estimated in Step 2 based on the following model;

$$V_{OC.GY,j}, \text{ are estimated in Step 2 based on the following model;}$$

$$\begin{cases} V_{OC.GY,j} = V_{GX,j} + \frac{n}{2}r(I_{GX,j} + I_{M,j(j+1)} - I_{M,(j-1)j} + I_{st}) \\ V_{OC.GY,j} = V_{GY,j} + \frac{n}{2}r(-I_{GY,j} + I_{st}) \end{cases}$$

(8)

The OCV of the *j*-th module,  $V_{OCMj}$ , is the sum of  $V_{OC,GXj}$  and  $V_{OC,GYj}$ . From (8),

$$V_{OC.M.j} = V_{OC.GX.j} + V_{OC.GY.j}$$

$$= V_{M.j} + \frac{n}{2}r(I_{GX.j} - I_{GY.j} + I_{M.j(j+1)} - I_{M.(j-1)j} + 2I_{st})$$

(9)

Step 3 judges whether modules and groups are balanced. If the OCV difference between adjacent modules or Group  $X_j$  and  $Y_j$  in each module exceeds a threshold voltage level, the module equalization starts. First, the absolute value of the OCV difference between adjacent modules (i.e.,  $|V_{OC.M.j} - V_{OC.M.(j+l)}|$ ) is calculated to be compared with the threshold level  $V_{M.th}$  of the module equalization. If  $|V_{OC.M.j} - V_{OC.M.(j+l)}| \ge V_{M.th}$  is yes, the operation moves to the next step. If no, the OCV difference between Group  $X_j$  and  $Y_j$  (i.e.,  $|V_{OC.GX.j} - V_{OC.GY.j}|$ ) is also

calculated to be compared with the threshold level  $V_{G.th}$  of the group equalization.

In Step 4, if either of  $|V_{OC.M.j} - V_{OC.M.(j+l)}| \ge V_{M.th}$  or  $|V_{OC.GX.j} - V_{OC.GY.j}| \ge V_{G.th}$  is detected, the CIDAB converter is enabled with properly setting both  $\varphi_{G.j}$  and  $\varphi_{M}$  depending on voltage imbalance conditions. For example, if  $V_{OC.M.j} > V_{OC.M.(j+l)}$ ,  $\varphi_{M}$  should be positive arbitrary value for the inter-module CIDAB converter to transfer power from j-th module to (j+1)-th one. If  $V_{OC.GX.j} < V_{OC.GY.j}$ ,  $\varphi_{G.j}$  should be negative so that the intramodule CIDAB converter delivers power from Group Y to X. On the other hand, if the calculated OCV differences are smaller than threshold levels, the CIDAB converter is disabled to stop the module equalization.

This course of the module equalization is performed for all modules until all module and group voltages are balanced.

#### V. DESIGN EXAMPLE

This section presents a design example of the CIDAB converter for LIB modules consisting of twelve cells connected in series. Component values are determined so that  $I_{X,j} = I_{Y,j} = 1.0$  A in the cell equalization mode and  $I_{XG,j} = I_{YG,j} = I_{M,f(j+1)} = I_{M,f(j+1)} = 1.0$  A in the module equalization mode when  $V_{Xcell,j} = V_{Ycell,j} = 4.2$  V and  $V_{XG,j} = V_{XG,f(j+1)} = V_{YG,j} = 25.2$  V (4.2V/cell). The switching frequency is  $f_s = 100$  kHz.

#### A. Inductance

Denominators in (1) and (3), which yield  $I_{X,j} = I_{Y,j}$  in the cell equalization mode and  $I_{XG,j} = I_{YG,j}$  in the module equalization mode, are the same, whereas  $V_{Xcell,j}$  and  $V_{Ycell,j}$  (= 4.2 V) in the nominator in (1) is one-sixth of  $V_{XG,j}$  and  $V_{YG,j}$  (= 25.2 V). Therefore,  $d_{\varphi G,j}$  in (1) must be rather larger than that in (3) in order to fulfill  $I_{X,j} = I_{Y,j} = 1.0$  A and  $I_{XG,j} = I_{YG,j} = 1.0$  A. Here,  $d_{\varphi G,j}$  is assumed to be 0.167 (i.e.,  $\varphi_{G,j} = 60^{\circ}$ ) in the cell equalization mode. From (1), L is determined as

$$L = \frac{4.2 \text{ V}}{2 \times 100 \text{ kHz} \times 1.0 \text{ A}} 0.167 |0.5 - 0.167|$$

$$\to L = 1.2 \text{ } \mu\text{H}$$

(10)

Voltage values in nominators (i.e.,  $V_{XG,j}$ ,  $V_{YG,j}$ , and  $V_{XG,(j+1)}$ ) in (3) and (4) are 25.4 V. Since (3) and (4) are expressed in the very similar form, operating the converter with  $d_{\phi M} = d_{\phi G,j} = 0.167$  is considered preferable. Applying  $d_{\phi M} = d_{\phi G,j} = 0.167$  into (3) and (4) yields

$$L_M = 1.2 \,\mu\text{H} \tag{11}$$

#### B. Capacitance

According to (1) and (3), the input and output currents of the CIDAB converter are dependent on L or  $L_M$  and are independent on capacitances of  $C_H$  and  $C_L$  or  $C_{MH}$  and  $C_{ML}$ , as long as these passive components do not resonate. To avoid resonant operations, capacitances of  $C_H$ ,  $C_L$ ,  $C_{MH}$ , and  $C_{ML}$  should be large enough so that the resonant frequency of L and the series connection of  $C_{H^-}$ - $C_L$  (or  $L_M$  and  $C_{MH^-}$ - $C_{ML}$ ) is at least lower than one-fifth of  $f_s$ . Given dc bias characteristics of ceramic capacitors, the capacitance C of  $C_H$ ,  $C_L$ ,  $C_{MH}$ , and  $C_{ML}$  should have enough margin. Here, C is determined to be 1.5 times larger than the theoretical value;

$$\frac{1}{2\pi\sqrt{\frac{LC}{2\times1.5}}} = \frac{f_s}{5} \to C = 160 \,\mu\text{F}$$

(12)

## C. Voltage Stress of Capacitors

In this subsection, all cell voltages and group voltages are assumed equal to be  $V_{cell}$  and  $V_G$ , respectively. In the cell equalization mode, voltages of  $C_H$  and  $C_L$ ,  $V_{CH}$  and  $V_{CL}$ , vary depending on which cells are selected.  $V_{CH}$  and  $V_{CL}$  become the highest when the most distantly located cells [e.g.,  $B_{X1}$  and  $B_{Y4}$  in the case of Fig. 6(a)] are selected. In the module equalization mode [see Fig. 6(b)], on the other hand,  $V_{CH}$  and  $V_{CL}$  are equal to the group voltage  $V_G$ .  $V_{CH}$  and  $V_{CL}$  in the cell and group equalization modes are summarized as

$$V_{CH}, V_{CL} = \begin{cases} (n-1)V_{cell} & (Cell\ Equalization) \\ V_M - V_{cell} & (Module\ Equalization) \end{cases}$$

(13)

where n is the number of cells in a module (i.e., n = 12 for the twelve-cell module). This equation suggests that  $V_{CH}$  and  $V_{CL}$  in the cell equalization mode are higher than those in the module equalization mode. According to the given design target, the voltage rating of  $C_H$  and  $C_L$  can be determined as

$$V_{CH}, V_{CL} = (12 - 1) \times 4.2 \text{ V} = 46.2 \text{ V} \rightarrow 100 \text{ V}$$

(14)

Since  $C_{MH}$  and  $C_{ML}$  are connected between adjacent Group X's, their voltages,  $V_{CMH}$  and  $V_{CML}$ , are equal to the module voltage  $V_{M}$ ;

$$V_{CMH}, V_{CML} = V_M = 50.4 \text{ V} \rightarrow 100 \text{ V}$$

(15)

From (14) and (15), ceramic capacitors with a rated voltage of 100 V are selected for  $C_H$ ,  $C_L$ ,  $C_{MH}$ , and  $C_{ML}$ .

#### VI. EXPERIMENTAL RESULTS

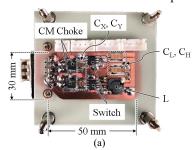

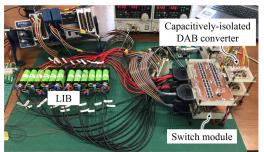

# A. Prototype

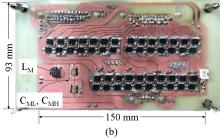

The proposed modular equalization system for two modules, each comprising twelve cells connected in series, was built. The CIDAB converter and switch module were separately built, and

Fig. 10. Photograph of (a) CIDAB converter and (b) switch module.

these were connected using D-sub connectors. The prototypes of the CIDAB converter and switch module are shown in Figs. 10(a) and (b), respectively. Circuit components are listed in Table I. The LC tank for the inter-module CIDAB converter ( $L_{\rm M}$ ,  $C_{\rm MH}$ , and  $C_{\rm ML}$ ) was mounted on the switch module board. The switches in the CIDAB converter were driven with 50% duty cycle at  $f_s = 100$  kHz.

## B. Characteristics of CIDAB Converter

Before performing equalization tests, characteristics of the CIDAB converter in the cell and module equalization modes were individually measured. In the cell equalization mode, Port X and Y of the CIDAB converter are connected to a cell through the switch module, as exemplified in Fig. 6(a). In the module equalization mode, on the other hand, whole Groups X and Y are connected to the CIDAB converter [see Fig. 6(b)]. Hence, the CIDAB converter was tested with  $V_{X,j} = V_{Y,j} = 4.2 \text{ V}$  and  $V_{XG,j} = V_{YG,j} = 25.2 \text{ V}$  (= 4.2 V × 6 cells) for the cell and module

TABLE I

COMPONENT LIST OF CIDAB CONVERTER AND SWITCH MODULE

|                    | Component                                                              | Value                                       |  |  |  |

|--------------------|------------------------------------------------------------------------|---------------------------------------------|--|--|--|

|                    | Qxh, Qxl, Qyh,Qyl                                                      | IRF7351PbF, $R_{on} = 17.8 \text{ m}\Omega$ |  |  |  |

| CIDAB<br>Converter | L                                                                      | 1.2 μΗ                                      |  |  |  |

|                    | $C_H, C_L$                                                             | Ceramic Capacitor, $10  \mu F \times 16$    |  |  |  |

|                    | $C_X, C_Y$                                                             | Ceramic Capacitor, 22 μF × 8                |  |  |  |

|                    | Common Mode Choke                                                      | DLW5BTM102SQ2L                              |  |  |  |

|                    | Gate Driver                                                            | UCC27201D                                   |  |  |  |

|                    | S <sub>X</sub> , S <sub>Y</sub> , S <sub>even</sub> , S <sub>odd</sub> | FDS2572, $R_{on} = 47 \text{ m}\Omega$      |  |  |  |

| Swith              | $L_{M}$                                                                | 1.2 μΗ                                      |  |  |  |

| Module             | C <sub>MH</sub> , CM <sub>L</sub>                                      | Ceramic Capacitor, 10 μF × 16               |  |  |  |

|                    | Gate Driver                                                            | Si8751AB-IS                                 |  |  |  |

Fig. 11. Measured output current characteristics of CIDAB converter in (a) cell equalization mode and (b) module equalization mode.

equalization modes, respectively.

Measured output current (i.e.,  $I_{Y,j}$ ) characteristics are shown in Fig. 11. The experimental results agreed very well with the theoretical characteristics, verifying the operation of the prototype of the CIDAB converter.

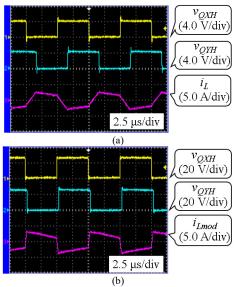

Fig. 12. Measured operation waveforms of CIDAB converter in (a) cell equalization mode with  $\varphi_{Gj} = 60^{\circ}$  and (b) module equalization mode with  $\varphi_M = 12^{\circ}$ .

Fig. 13. Measured power conversion efficiencies of CIDAB converter in (a) cell equalization mode and (b) module equalization mode.

Measured waveforms in the cell equalization mode with  $\varphi_{G,j} = 60^{\circ}$  and the module equalization mode with  $\varphi_M = 12^{\circ}$  are shown in Figs. 12(a) and (b).  $I_{Y,j}$  was nearly 1.0 A in both cases, but the current slope in the module equalization mode was steeper because of the higher input and output voltages of 25.2 V

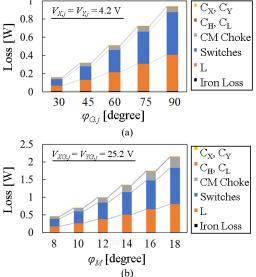

The measured power conversion efficiencies in the cell and module equalization modes are shown in Figs. 13(a) and (b), respectively. Theoretical efficiencies calculated based on loss models are also shown—the theoretical loss model is discussed in the following paragraph. Similar to traditional transformer-based DAB converters, the measured efficiencies of the CIDAB converter decreased with  $\varphi_{G,j}$  and  $\varphi_M$  due to increased circulating currents. The measured and calculated efficiencies agreed well, verifying the loss models.

The loss breakdowns estimated by the theoretical loss models are shown in Fig. 14. Switching losses were assumed zero thanks to the ZVS operations. Except for the iron loss, all losses were Joule losses, which were the product of resistance and the square of an rms current. The iron loss of L was calculated based on Steinmetz's equation [58]. The Joule losses of L, C<sub>H</sub>, and C<sub>L</sub> were calculated using an rms current of L,  $I_{L,rms}$ . Since every switch conducts during half the switching period, the rms switch currents are equal to  $I_{X,j}$  and  $I_{Y,j}$  in the cell equalization mode (3) or  $I_{XG,j}$  and  $I_{YG,j}$  in the module equalization mode (4). The rms currents of C<sub>X</sub> and C<sub>Y</sub> were obtained from the simulation analysis.

The estimated breakdowns revealed that Joule losses of the switches and inductors were dominant while losses of capacitors were negligibly small. Hence, employing switches and inductors with lower resistance is an effective way to improve the power conversion efficiencies.

Fig. 14. Estimated loss breakdowns of CIDAB converter in (a) cell equalization mode and (b) module equalization mode.

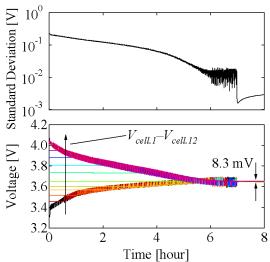

Fig. 15. Resultant voltage and standard deviation profiles of twelve cells in cell equalization mode.

# C. Cell Equalization

The cell equalization test was performed using twelve cylindrical cells, each with a typical capacity of 3350 mAh (NCR18650B, Panasonic). Initial OCVs were intentionally imbalanced in the range of 3.31–4.07 V, corresponding to the state-of-charge variation of 2%–96%. The cell equalization was performed with  $\varphi_{G,j}=\pm 60^{\circ}$  and  $V_{cell.th}=10$  mV. A compact data acquisition system (Compact DAQ, National Instruments) with voltage input modules (NI-9221) and digital I/O modules (NI-9403) was used as a control platform. The equalization algorithm (see Fig. 8) was implemented with LabVIEW.

The resultant cell equalization profiles are shown in Fig. 15. Cells with high initial voltages supplied power to the CIDAB converter, and their voltage decreased. At the same time, cells with low initial voltages received power from the CIDAB converter, and their voltage increased. Thanks to this energy redistribution through the CIDAB converter, cell voltages gradually converged, and the voltage imbalance decreased as low as 8.3 mV. The calculated standard deviation of cell voltages at the end of the cell equalization test was 2.9 mV, demonstrating the cell equalization performance of the proposed equalizer.

# D. Module Equalization

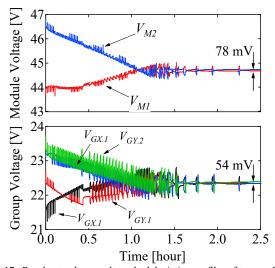

The module equalization test was performed for two modules, each consisting of twelve cells connected in series. The experimental setup is shown in Fig. 16. Initial OCVs of the modules and groups were imbalanced in the range of 43.63–46.82 V and 20.95–23.71 V, respectively. The module equalization test was performed with  $\varphi_{G,j} = \varphi_M = \pm 12^\circ$  and  $V_{M.th} = V_{G.th} = 80 \text{ mV}$ .

The recorded module equalization profiles are shown in Fig. 17. The module and group voltages converged simultaneously. Group and module voltages were nearly equalized at 1.6 hours. The voltage mismatches of the groups and modules decreased

Fig. 16. Experimental setup for module equalization test using two LIB modules, each consisting of twelve cells connected in series.

Fig. 17. Resultant voltage and standard deviation profiles of two modules in module equalization mode.

as low as 54 and 78 mV, respectively, at the end of the test, thus sufficiently eliminating the voltage imbalance.

# VII. COMPARISON WITH CONVENTIONAL EQUALIZERS

This section compares the proposed and conventional equalizers from the viewpoint of component counts and reported efficiency. Since the proposed modular equalization system consists of two levels (i.e., the cell-level equalization in each module and module-level equalization), the comparison is performed not only for the system but also for intra-module equalizers.

Since each switch requires an auxiliary circuit, including a driver and its power supply, the switch count can be a good index to represent the circuit complexity. The circuit volume is chiefly dependent on passive component counts, especially bulky magnetic component counts. Equalization speed or time, on the other hand, cannot be fairly compared and hence is excluded from the comparison because it is dependent on various factors, such as numbers of cells and modules, initial imbalance condition, equalization current, cell capacity, etc.

The intra-module equalizer in a single module in the proposed system is compared with conventional equalizers using selection switches, as shown in Table II where n is the cell count. Conventional equalizers based on flyback converters

|             | IABLEII           |                     |       |

|-------------|-------------------|---------------------|-------|

| ENT INTED A | MODULE FOLLALIZED | AND CONTRIBUTION AT | POLLA |

| COMPARISON BETWEEN INTRA-MODULE EQUALIZER AND CONVENTIONAL EQUALIZERS |                        |                     |                                           |                                    |        |             |                        |

|-----------------------------------------------------------------------|------------------------|---------------------|-------------------------------------------|------------------------------------|--------|-------------|------------------------|

| Topology                                                              | Switch                 | Selection<br>Switch | L                                         | $C^{\dagger\dagger\dagger\dagger}$ | D      | Transformer | Reported<br>Efficiency |

| [31]                                                                  | 2                      | 2 <i>n</i>          | -                                         | -                                  | 2      | 2           | -                      |

| [32]                                                                  | 1                      | n +5                | 1                                         | 1                                  | 1      | 1           | -                      |

| [33]                                                                  | 2                      | 2 <i>n</i>          | 1                                         | ı                                  | 2      | 2           | -                      |

| [34]                                                                  | 2                      | 2n+10               | 2                                         | 3                                  | 2      | -           | 60%                    |

| [35]                                                                  | 2(n+1)                 | -                   | 1                                         | -                                  | 2(n+1) | -           | -                      |

| [36]                                                                  | $4\mathrm{BS}^\dagger$ | n+1 ††              | 1                                         | 1                                  | -      | -           | 80%                    |

| [37]                                                                  | $2\mathrm{BS}^\dagger$ | n+1 ††              | -                                         | 1                                  | 1      | 1           | 80.4%                  |

| [39]                                                                  | 4 BS <sup>†</sup>      | 2 <i>n</i>          | 1                                         | 1                                  | -      | -           | 87.9% (peak)           |

| [40]                                                                  | 5                      | 2(n+1) Relays       | 2                                         | 1                                  | 4      | -           | -                      |

| Proposed                                                              | 4                      | n+12                | $1 (L) + 2 (CMC^{\dagger\dagger\dagger})$ | 2                                  | -      | -           | 84% (average)          |

<sup>†</sup> BS (bidirectional switch), †† Must operate at high frequency

TABLE III COMPARISON BETWEEN PROPOSED AND CONVENTIONAL MODULAR EQUALIZATION SYSTEMS

| Topology | Module Equalizer                           | Cell Equalizer                     | Switch           | Selection<br>Switch | L                                   | $C^{\dagger\dagger}$ | D  | Transformer                 | Reported Efficiency               |

|----------|--------------------------------------------|------------------------------------|------------------|---------------------|-------------------------------------|----------------------|----|-----------------------------|-----------------------------------|

| [28]     | Forward Converter                          | Flyback Converter                  | m                | mn                  | -                                   | -                    | n  | mn + m                      | 81.6% (average)                   |

| [29]     | SCC                                        | SCC                                | 2mn + 2m         | -                   | -                                   | m(n-1) + (m-1)       | -  | -                           | -                                 |

| [29]     | SCC                                        | Multi-Winding<br>Flyback Converter | 3 <i>m</i>       | -                   | -                                   | m-1                  | mn | m (n Secondary Windings)    | -                                 |

| [42]     | PWM Converter                              | PWM Converter                      | 2m(n-1) + 2(m-1) | -                   | m(n-1) + (m-1)                      | -                    | -  | -                           | -                                 |

| [43]     | Multidirectional<br>Multiport<br>Converter | PWM Converter                      | 2m(n-1)<br>+2m   | -                   | m (n-1)                             | 2 <i>m</i>           | -  | 1 (m Secondary<br>Windings) | 89.7% (average)                   |

| [45]     | Flyback Converter                          | Flyback Converter                  | mn               | -                   | -                                   | 1                    |    | m (n Secondary Windings)    | 89.4% (peak)                      |

| [47]     | Forward Converter                          | Forward Converter                  | mn               | ı                   | ı                                   | ı                    | 1  | m (n Secondary Windings)    | 95.6% (peak)                      |

| [48]     | SCC                                        | Multi-Winding<br>Flyback Converter | mn + 2m          | -                   | -                                   | m-1                  | m  | m (n Secondary Windings)    | 83.3% (average)                   |

| Proposed | CIDAB Converter                            | CIDAB Converter                    | 4 <i>m</i>       | m (n+12)            | 2m-1 (L) + $2m$ (CMC <sup>†</sup> ) | 2(2m-1)              | 1  | -                           | Cell: 84% (average)<br>Module: 96 |

CMC (common mode choke), †† Smoothing capacitors excluded

[31]-[33] need a transformer, and therefore these topologies would be bulky. Transformerless topologies [34], [39], [40] contain 2n selection switches, and their circuit complexity is prone to soar as n increases. Although the equalizers of [36], [37] can reduce the number of selection switches as low as n+1, high-frequency gate drivers are necessary to drive these selection switches, likely increasing the complexity and cost of drive circuits. Meanwhile, the intra-module equalizer in the proposed system is transformerless, and its selection switches can operate at a low frequency, similar to those in [31]–[35]. In comparison with the conventional equalizers with 2n selection switches from the viewpoint of the selection switch count, the proposed intra-module equalizer is advantageous for modules comprising more than twelve cells.

The proposed modular equalization system is compared with conventional modular systems, as shown in Table III where m is the module count. Most of the conventional systems are based on isolated converters, such as flyback converters and forward

converter, and require transformers or multi-winding transformers that lead to the increased circuit volume, cost, and design difficulty. Although the conventional systems in [29], [42] are transformerless, passive component counts are proportional to n, likely increasing the circuit volume. The proposed modular equalization system, on the other hand, not only is transformerless but also can reduce the passive component count, and therefore would be advantageous to achieve circuit miniaturization. Although m(n+12) selection switches are necessary, these switches can be slow and do not need high-frequency gate drivers.

## VIII. CONCLUSIONS

This paper has proposed the modular equalization system consisting of multiple LIB modules connected in series. Cells in each module are subdivided into two groups, and each module contains a selection switch module and an intra-module CIDAB converter that performs direct cell-to-cell equalization. The switching legs of adjacent modules' CIDAB converters are

<sup>†††</sup> CMC (common mode choke), †††† Smoothing capacitors excluded

connected through an LC tank to configure an inter-module equalizer that performs the module equalization. Based on the DPS control technique, the PS angles of both the intra- and inter-module CIDAB converters are manipulated to perform the cell and module equalization. The proposed equalization system offers good scalability as the design of the intra-module equalizer is fixed while inter-module equalizers can be configured without the need for additional active switches.

The proposed modular equalization system operates either in the cell or module equalization modes, and these modes do not coincide. In the cell equalization mode, the target cells in each module are determined based on calculated SOCs and are selected by the switch module. The intra-module CIDAB converter transfers power between the selected target cells to perform cell equalization. In the module equalization mode, on the other hand, whole groups are selected in each module, and both the intra- and inter-module CIDAB converters simultaneously operate to perform the module equalization.

The experimental prototype for two LIB modules, each consisting of twelve cells connected in series, was built. The cell and module equalization tests were separately carried out from voltage imbalanced conditions. The cell and module voltages were sufficiently equalized, demonstrating the equalization performance of the proposed modular equalization system.

#### REFERENCES

- B. Kenney, K. Darcovich, D. D. MacNeil, I. J. Davidson, "Modelling the impact of variations in electrode manufacturing on lithium-ion battery modules," *J. Power Sources*, vol. 213, no. 1, pp. 391–401, Sep. 2012.

- [2] L. Zhou, Y Zheng, M. Ouyang, and L. Lu, "A study on parameter variation effects on battery packs for electric vehicles," *J. Power Sources*, vol. 364, no. 1, pp. 242–252, Oct. 2017.

- [3] K.C. Chiu, C.H. Lin, S.F. Yeh, Y.H. Lin, C.S. Huang, and K.C. Chen, "Cycle life analysis of series connected lithium-ion batteries with temperature difference," *J. Power Sources*, vol. 263, no. 1, pp. 75–84, Oct. 2014.

- [4] Q. Xia, Z. Wang, Y. Ren, B. Sun, D. Yang, and Q. Feng, "A reliability design method for a lithium-ion battery pack considering the thermal disequilibrium in electric vehicles," *J. Power Sources*, vol. 386, pp. 10– 20, May 2018.

- [5] P.A. Cassani and S.S. Williamson, "Design, testing, and validation of a simplified control scheme for a novel plug-in hybrid electric vehicle battery cell equalizer," *IEEE Trans. Ind. Electron.*, vol. 57, no. 12, pp. 3956–3962, Dec. 2010.

- [6] T.H. Phung, A. Collet, and J. Crebier, "An optimized topology for next-to-next balancing of series-connected lithium-ion cells," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4603–4613, Sep. 2014.

[7] J. Ewanchuk and J. Salmon, "A modular balancing bridge for series

- [7] J. Ewanchuk and J. Salmon, "A modular balancing bridge for series connected voltage sources," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4712–4722, Sep. 2014.

- [8] A. Baughman and M. Ferdowsi, "Double-tiered switched-capacitor battery charge equalization technique," *IEEE Trans. Ind. Appl.*, vol. 55, no. 6, pp. 2277–2285, Jun. 2008.

- [9] M. Uno and K. Tanaka, "Influence of high-frequency charge-discharge cycling induced by cell voltage equalizers on the life performance of lithium-ion cells," *IEEE Trans. Veh. Technol.*, vol. 60, no. 4, pp. 1505– 1515, May 2011.

- [10] Y. Yuanmao, K.W.E. Cheng, and Y.P.B. Yeung, "Zero-current switching switched-capacitor zero-voltage-gap automatic equalization system for series battery string," *IEEE Trans. Power Electron.*, vol. 27, no. 7, pp. 3234–3242, Jul. 2012.

- [11] M.Y. Kim, C.H. Kim, J.H. Kim, and G.W. Moon, "A chain structure of switched capacitor for improved cell balancing speed of lithium-ion

- batteries," *IEEE Trans. Ind. Electron.*, vol. 61, no. 9, pp. 3989–3999, Aug. 2014

- [12] Y. Shang, B. Xia, F. Lu, C. Zhang, N. Cui, and C.C. Mi, "A switched-coupling-capacitor equalizer for series-connected battery strings," *IEEE Trans. Power Electron.*, vol. 32, no. 10, pp. 7694–7706, Oct. 2017.

- [13] Y. Shang, Q. Zhang, N. Cui, and C. Zhang, "A cell-to-cell equalizer based on three-resonant-state switched-capacitor converters for seriesconnected battery strings," *Energies*, vol.10, no. 206, 2017.

- [14] N.H. Kutkut, D.M. Divan, and D.W. Novotny, "Charge equalization for series connected battery strings," *IEEE Trans. Ind. Appl.*, vol. 31, no. 3, pp. 562–568, May/Jun. 1995.

- [15] M. Uno and K. Tanaka, "Single-switch cell voltage equalizer using multistacked buck-boost converters operating in discontinuous conduction mode for series-connected energy storage cells," *IEEE Trans.* Veh. Technol., vol. 60, no. 8, pp. 3635–3645, Oct. 2011.

- [16] M. Uno and K. Tanaka, "Double-switch single-transformer cell voltage equalizer using a half-bridge inverter and voltage multiplier for seriesconnected supercapacitors," *IEEE Trans. Veh. Technol.*, vol. 61, no. 9, pp. 3920–3930, Nov. 2012.

- [17] M. Uno and K. Tanaka, "Double-switch single-transformer cell voltage equalizer using a half-bridge inverter and voltage multiplier for seriesconnected supercapacitors," *IEEE Trans. Power Electron.*, vol. 61, no. 9, pp. 3920–3930, Nov. 2012.

- [18] M. Uno and A. Kukita, "Double-switch equalizer using parallel- or seriesparallel-resonant inverter and voltage multiplier for series-connected supercapacitors," *IEEE Trans. Power Electron.*, vol. 29, no. 2, pp. 812– 828, Feb. 2014.

- [19] M. Uno and A. Kukita, "Single-switch single-transformer cell voltage equalizer based on forward-flyback resonant inverter and voltage multiplier for series-connected energy storage cells," *IEEE Trans. Veh. Technol.*, vol. 63, no. 9, pp. 4232–4247, Nov. 2014.

- [20] M. Arias, J. Sebastian, M.M. Hernando, U. Viscarret, and I. Gil, "Practical application of the wave-trap concept in battery-cell equalizers," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5616–5631, Oct. 2015.

- [21] M. Uno and A. Kukita, "String-to-battery voltage equalizer based on half-bridge converter with multi-stacked current doublers for series-connected batteries," *IEEE Trans. Power Electron.*, vol. 34, no. 2, pp. 1286–1298, Feb. 2019

- [22] A. Xu, S. Xie, and X. Liu, "Dynamic voltage equalization for seriesconnected ultracapacitors in EV/HEV applications," *IEEE Trans. Veh. Technol.*, vol. 58, no. 8, pp. 3981–3987, Oct. 2009.

- [23] S. Li, C.C. Mi, and M. Zhang, "A high-efficiency active battery-balancing circuit using multiwinding transformer," *IEEE Trans. Ind. Appl.*, vol. 49, no. 1, pp. 198–3207, Jan./Feb. 2013.

- [24] C.C. Hua, Y.H. Fang, Y.L. Chen, "Modified rectifications for improving the charge equalisation performance of series-connected battery stack," *IET Trans. Power Electron.*, vol. 9, no. 9, pp. 1924–1932, 2016.

- [25] M. Uno and K. Kukita, "Bidirectional PWM converter integrating cell voltage equalizer using series-resonant voltage multiplier for seriesconnected energy storage cells," *IEEE Trans. Power Electron.*, vol. 30, no. 6, pp. 3077–3090, Jun. 2015.

- [26] K. Yashiro and M. Uno, "Transformer-less bidirectional PWM converter integrating voltage multiplier-based cell voltage equalizer for seriesconnected electric double-layer capacitors," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4304–315, May 2019.

- [27] C.H. Kim, H.S. Park, C.E. Kim, G.W. Moon, and J.H. Lee, "Individual charge equalization converter with parallel primary winding of transformer for series connected lithium-ion battery strings in an HEV," *J. Power Electron.*, vol. 9, no. 3, pp. 472–480, May 2009.

- [28] H.S. Park, C.E. Kim, C.H. Kim, G.W. Moon, and J.H. Lee, "A modularized charge equalizer for an HEV lithium-ion battery string," *IEEE Trans. Ind. Electron.*, vol. 56, no. 5, pp. 1464–1476, May 2009.

- [29] H.S. Park, C.H. Kim, K.B. Park, G.W. Moon, and J.H. Lee, "Design of a charge equalizer based on battery modularization," *IEEE Trans. Veh. Technol.*, vol. 58, no. 7, pp. 3216–3223, Sep. 2009.

- [30] C.H. Kim, M.Y. Kim, H.S. Park, and G.W. Moon, "A modularized two-stage charge equalizer with cell selection switches for series-connected lithium-ion battery string in a HEV," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3764–3774, Aug. 2012.

- [31] C.H. Kim, M.Y. Kim, and G.W. Moon, "A modularized charge equalizer using a battery monitoring IC for series-connected Li-ion battery strings

# > REPLACE THIS LINE WITH YOUR PAPER IDENTIFICATION NUMBER (DOUBLE-CLICK HERE TO EDIT) <

- in electric vehicles," *IEEE Trans. Power Electron.*, vol. 28, no. 8, pp. 3779–3787, Aug. 2013.

- [32] M.M. Hoque, M.A. Hannan, A. Mohamed, and A. Ayob, "Battery charge equalization controller in electric vehicle applications: a review," *Renewable and Sustainable Energy Reviews*, vol. 75, pp. 1363–1385, Aug. 2017.

- [33] M.A. Hannan, M.M. Hoque, P.J. Ker, R.A. Begumm, and A. Mohamed, "Charge equalization controller algorithm for series-connected lithiumion battery storage systems modeling and applications," *Energies*, vol. 10, no. 9, pp. 1–20, Sep. 2017.

- [34] M. Uno, K. Yoshino, and K. Hasegawa, "Direct cell-to-cell voltage equalizer using capacitively-isolated parallel-resonant converter for series-connected Energy storage cells," in Proc. IEEE 18th Int. Power Electron. Motion Control Conf. (PEMC), pp. 94–100, Aug. 2018.

- [35] S. Yarlagadda, T.T. Hartley, and I. Husain, "A battery management system using an active charge equalization technique based on a DC/DC converter topology," *IEEE Trans. Ind. Appl.*, vol. 49, no. 6, pp. 2720– 2729, Nov./Dec. 2013.

- [36] K.M. Lee, Y.C. Chung, C.H. Sung, and B. Kang, "Active cell balancing of Li-ion batteries using LC series resonant circuit," *IEEE Trans. Ind. Electron.*, vol. 62, no. 9, pp. 5491–5501, Sep. 2015.

- [37] K.M. Lee, S.W. Lee, Y.G. Choi, and B. Kang, "Active balancing of Liion battery cells using transformer as energy carrier," *IEEE Trans. Ind. Electron.*, vol. 64, no. 2. pp. 1251–1257, Feb. 2017.

- [38] S.W. Lee, K.M. Lee, Y.G. Choi, and B. Kang, "Modularized design of active charge equalizer for Li-ion battery pack," *IEEE Trans. Power Electron.*, vol. 65, no. 11, pp. 8697–8706, Nov. 2018.

- [39] Y. Shang, Q. Zhang, N. Cui, B. Duan, Z. Zhou, and C. Zhang, "Multi-cell-to-multi-cell equalizers based on matrix and half-bridge LC converters for series-connected battery strings," *IEEE JESTPE*, to be published.

- [40] Y. Shang, C. Zhang, N. Cui, and J.M. Guerrero, "A cell-to-cell battery equalizer with zero-current switching and zero-voltage gap based on quasi-resonant LC converter and boost converter," *IEEE Trans. Power Electron.*, vol. 30, no. 7, pp. 3731–3747, Jul. 2015.

- [41] H. Chen, L. Zhang, and Y. Han, "System-theoretic analysis of a class of battery equalization systems: mathematical modeling and performance evaluation," *IEEE Trans. Veh. Technol*, vol. 64, no. 4, pp. 1445–1457, Apr. 2015.

- [42] B. Dong, Y. Li, and Y. Han, "Parallel architecture for battery charge equalization," *IEEE Trans. Power Electron.*, vol. 30, no. 9, pp. 4906– 4913, Sep. 2015.

- [43] Z. Zhang, H. Gui, D.J. Gu, Y. Yang, and X. Ren, "A hierarchical active balancing architecture for lithium-ion batteries," *IEEE Trans. Power Electron.*, vol. 32, no. 4, pp. 2757–2768, Apr. 2017.

- [44] C. Hua and Y.H. Fang, "A charge equalizer with a combination of APWM and PFM control based on a modified half-bridge converter," *IEEE Trans. Ind. Electron.*, vol. 31, no. 4, pp. 2970–1979, Apr. 2016.

- [45] Y. Shang, B. Xia, C. Zhang, N. Cui, J. Yang, and C.C. Mi, "An automatic equalizer based on forward-flyback converter for series-connected battery strings," *IEEE Trans. Ind. Electron.*, vol. 64, no. 7, pp. 5380–5391, Jul. 2017

- [46] C. Zhang, Y. Shang, Z. Li, and N. Cui, "An interleaved equalization architecture with self-learning fuzzy logic control for series-connected battery strings," *IEEE Trans. Veh. Technol.*, vol.66, no. 12, pp. 10923– 10934, Dec. 2017.

- [47] Y. Shang, N. Cui, B. Duan, and C. Zhang, "A global modular equalizer based on forward conversion for series-connected battery strings," *IEEE J. Emerging and Selected Topics in Power Electron.*, vol. 6, no. 3, pp. 1456–1469, Sep. 2018.

- [48] T.M. Bui, C.H. Kim, K.H. Kim, and S.B. Rhee, "A modular cell balancer based on multi-winding transformer and switched-capacitor circuits for a series-connected battery string in electric vehicles," *Applied Science*, vol. 8, no. 8, pp. 1–21, Aug. 2018.

- [49] J. Cao, N. Schofield, and A. Emadi, "Battery balancing methods: a comprehensive review," in Proc. *IEEE Veh. Power Propulsion Conf.*, pp. 1–6, Sep. 2008.

- [50] S.R. Sanders, E. Alon, H.P. Le, M.D. Seeman, M. Jhon, and V.W. Ng, "The road to fully integrated dc-dc conversion via the switched-capacitor approach," *IEEE Trans. Power Electron.*, vol. 28, no. 9, pp. 4146–4155, Sep. 2013.

- [51] M. Uno and A. Kukita, "PWM switched capacitor converter with switched-capacitor-inductor cell for adjustable high step-down voltage conversion," *IEEE Trans. Power Electron.*, vol. 34, no. 1, pp. 425–437, Jan. 2019.

- [52] Y. Hayashi, Y. Matsugaki, and T. Ninomiya, "Capacitively isolated multicell dc-dc transformer for future dc distribution system," *IEEJ Journal Ind. Appl.*, vol. 6, no. 4, pp. 268–277, Apr. 2017.

- [53] H. Funato, K. Amano, T. Hatsumi, and J. Haruna, "Transfer power analysis of capacitively isolated outlet and plug (CapIsOP) using series resonance," in Proc. IEEE Int. Power Electron. Conf. (IPEC-Niigata 2018, ECCE Asia), pp. 1–6, May 2018.

- [54] J. W. Kimball, B.T. Kuhn, and P.T. Krein, "Increased performance of battery packs by active equalization," in Proc. *IEEE Veh. Power Propulsion Conf.*, pp. 323–327, Sep. 2007.

- [55] D. Andrea, Battery Management Systems for Large Lithium-Ion Battery Packs, Boston: Artech House, 2010, ch.3.2.3.3.

- [56] S.W. Lee, K.M. Lee, Y.G. Choi, and B. Kang, "SOC estimation of lithium-ion battery pack considering balancing Current," *IEEE Trans. Power Electron.*, vol. 33, no. 3, pp. 2216–2226, Mar. 2018.

- [57] T. Kim, W. Qiao, and L. Qu, "Power electronics-enabled self-X multicell batteries a design toward smart batteries," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4723–4733, Nov. 2012.

- [58] A.V. D. Bossche and V. C. Valchev, Inductors and Transformers for Power Electronics. Boca Raton, FL, USA: CRC Press, 2005, ch.2.1.

Masatoshi Uno (M'06) was born in Japan in 1979. He received the B.E. degree in electronics engineering and the M.E. degree in electrical engineering from Doshisha University, Kyoto, Japan, and the Ph.D. degree in space and astronautical science from the Graduate University for Advanced Studies, Hayama, Japan, in 2002, 2004, and 2012, respectively.

In 2004, he joined the Japan Aerospace Exploration Agency, Sagamihara, Japan, where he

developed spacecraft power systems including battery, photovoltaic, and fuel cell systems. In 2014, he joined the Department of Electrical and Electronics Engineering, Ibaraki University, Ibaraki, Japan, where he is currently an Associate Professor of Electrical Engineering.

His research interests include switching power converters for renewable energy systems, life evaluation for EDLCs and lithium-ion batteries, and development of spacecraft power systems. Dr. Uno received the Isao Takahashi Power Electronics Award in 2018.

**Koji Yoshino** was born in Japan in 1996. He received the B.E. degree and M.E degree in electrical engineering from Ibaraki University, Ibaraki, Japan, in 2018 and 2020, respectively.

Since 2020, he has been with Panasonic corporation. His research interests include cell voltage equalizers for lithium-ion batteries.