# Modular Equalization System Based on Star-Connected Phase-Shift Switched Capacitor Converters with Inherent Constant Current Characteristics for Electric Double-Layer Capacitor Modules

Masatoshi Uno, Member, IEEE, Koki Hasegawa

Abstract—This paper presents a modular equalization system integrating module- and cell-level voltage equalizers for energy storage systems consisting of series-connected modules, each comprising multiple cells connected in series. Star-connected phase-shift switched capacitor converters (PS-SCCs) and tappedinductor-based resonant voltage multiplier (TI-RVM) are employed as a module- and cell-level equalizers, respectively. The module- and cell-level equalizers are integrated with sharing active switches, hence halving the total switch count and achieving reduced system cost and complexity in comparison with conventional systems. In addition, equalization currents in both the PS-SCC and TI-RVM can be inherently constant regardless of voltage imbalance conditions, offering intrinsic current limitation capability at both the module and cell levels. An experimental equalization test was performed using the prototype for five electric double-layer capacitor (EDLC) modules, each containing six cells connected in series. Module and cell voltages were equalized at different rates, and voltage imbalance was eventually eliminated even during cycling, demonstrating the equalization performance of the proposed modular equalization system.

Keywords—Electric double-layer capacitor (EDLC), modularization, phase-shift switched capacitor converter (PS-SCC), voltage equalization.

#### I. INTRODUCTION

The advent of renewable energy sources has ignited the rapid expansion of applications and energy capacity of energy storage systems based on lithium-ion batteries and electric double-layer capacitors (EDLCs). Nowadays, such energy storage devices can be found anywhere from small portable electric devices to large-scale systems, including electric vehicles and utility-scale energy storage systems. Multiple energy storage cells are connected in series to meet voltage requirements of loads, but a variety of challenges originate from a characteristic mismatch of series-connected cells.

In a voltage-mismatched energy storage module consisting of series-connected cells, some cells with higher/lower voltages might be over-charged/-discharged during cycling. Charging and discharging cells beyond safety boundaries (i.e., upper and lower voltage limits) would cause not only premature irreversible degradation but also hazardous consequences such as fire or, in the worst case, explosion. Hence, charging and discharging of the energy storage module as a whole must be halted before any cells reach safety boundaries, but cells in the module can no longer be fully charged nor discharged. To fully exploit life performance and to utilize stored energies of such energy storage systems, individual voltages of series-connected cells need to be balanced.

Various kinds of cell voltage equalizers have been developed and commercialized [1], [2]. Adjacent cell-to-cell equalizers, such as bidirectional PWM converters [3]–[5] and switched capacitor converters (SCCs) [6]–[11], transfer energies between adjacent two cells. These equalizers can be flexibly applied to any number of cells without redesigning, but power conversion losses are prone to collectively soar because the power transfer is limited only between adjacent cells. Pack-to-cell equalizers that are essentially a single-input–multi-output converter can drastically simplify the circuit because their switch count can be a few regardless of the number of cells [12]–[24]. However, the poor design flexibility is cited as their drawback because these pack-to-cell equalizers need to be redesigned to be applied to a different number of cells.

Equalizers with selection switches have been developed mainly for automotive applications where several tens of cells are connected in series [25]–[34]. The number of converters as well as passive elements can be greatly reduced, realizing reduced circuit volume. However, numerous bidirectional switches are necessary, unavoidably resulting in increased circuit complexity. Cascaded equalization systems, in which each cell is equipped with a bidirectional converter, are fully extendable and offer operational redundancy [35]–[38]. In spite of their good modularity, the circuit complexity and cost are expected to soar as each cell essentially requires a bidirectional converter.

For large-scale energy storage systems, modular design has become mainstream as it can improve the scalability and facilitate the system assembly. Such systems consist of multiple

This paper is an extension of a conference paper entitled "Simple modular equalization system with reduced switch count and constant current characteristics for series-connected EDLC modules" at *IEEE Int. Conf. Power Electron. (ICPE), ECCE-Asia, Busan, Korea, May 27–30, 2019.*

M. Uno is with the College of Engineering, Ibaraki University, Hitachi 316-8511, Japan (e-mail: masatoshi.uno.ee@vc.ibaraki.ac.jp).

K. Hasegawa is with Seiko Epson Corporation, Nagano, Japan (e-mail: Hasegawa.Koki@exc.epson.co.jp).

series- and parallel-connected modules, each comprising several cells connected in series or parallel. In such modular energy storage systems, not only individual cell voltages in each module but also module voltages need to be balanced to unify all cell voltages in the systems. Different equalizer topologies can be employed for module- and cell-level equalizers, depending on applications and requirements. In large-scale systems, for example, temperature mismatch among modules tends to be relatively significant due to their large geometry [55], [56], and therefore, equalizers capable of relatively large equalization currents would be necessary for module-level equalization—large temperature mismatch leads to nonuniform self-discharge of modules, exacerbating voltage imbalance among modules. Meanwhile, cell temperatures in each module can easily be uniform thanks to their small geometries, thus equalizers with small equalization currents would be sufficient for cell-level equalization.

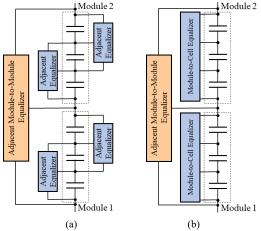

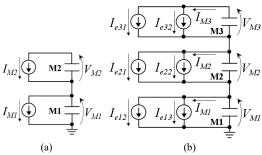

Equalization architectures for modular systems have been proposed [39]–[47]. Cell- and module-level equalizers are separately used in ordinary modular systems, as illustrated in Fig. 1, hence increasing the system complexity and cost. These modular systems also have an issue of the collective power conversion loss because of adjacent module-level equalizers—power transfer is limited only between adjacent modules. Furthermore, since energy storage cells are essentially a voltage source, both the module- and cell-level equalizers should desirably exhibit constant current characteristics without feedback control in order to avoid excessive currents.

In our previous study [48], the modular equalization system integrating the cell- and module-level equalizers with inherent constant current characteristics have been proposed for EDLCs. This paper presents the fully developed work of [48]. The proposed modular equalization system consists of star-connected phase-shift (PS) SCC-based module equalizers and tapped-inductor resonant voltage multiplier (TI-RVM)-based cell-level equalizers. Not only can any modules transfer power directly but also currents in both PS-SCC and TI-RVM can be automatically limited due to inherent constant current characteristics.

Fig. 1. Conventional modular equalization systems with separate module and cell equalizers. (a) Adjacent module-to-module and adjacent cell-to-cell equalizers. (b) Adjacent module-to-module and module-to-cell equalizers.

The rest of this paper is organized as follows. Section II describes the proposed modular equalization system and its major benefits. Detailed operation analyses for the TI-RVM and star-connected PS-SCC will be performed separately in Section III, in which the star-connected PS-SCC is transformed into a delta-connected one in order to simplify the analysis. Section IV discusses the control strategy, followed by the design example in Section V. Section VI derives a dc equivalent circuit of the modular equalization system and presents its equalization profiles. The results of experimental verification tests using a prototype for five EDLC modules, each comprising six cells, will be presented in Section VII. Section VIII presents the quantitative comparison between the proposed and conventional equalization systems from the viewpoint of component counts and reported efficiency.

#### II. PROPOSED MODULAR EQUALIZATION SYSTEM

#### A. Key Elements for Proposed Modular Equalizer

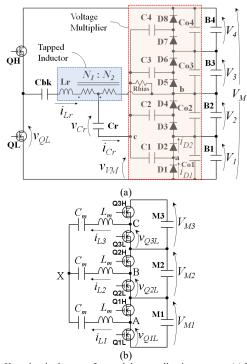

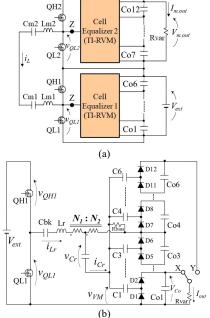

The proposed modular equalization system comprises two key elements shown in Figs. 2(a) and (b).

The TI-RVM, shown in Fig. 2(a), is a single-input–multi-output converter that functions as a cell-level equalizer.  $C_{bk}$  is a dc blocking capacitor. A bias resistor  $R_{bias}$  is used to stabilize voltages of the resonant capacitor  $C_r$  and coupling capacitors  $C_1$ – $C_4$ . Switches  $Q_H$  and  $Q_L$  alternately conduct in a complementary manner with a fixed duty cycle of 0.5. A square wave voltage generated by the switching leg is divided by the TI, by which the voltage multiplier is driven. The TI's leakage inductance  $L_r$  resonates with  $C_r$ , and output currents of the TI-RVM can be inherently constant when resonant currents are

Fig. 2. Key circuit elements for modular equalization system: (a) Tapped-inductor resonant voltage multiplier. (b) Star-connected phase-shift SCC.

discontinuous, as will be detailed in Section III-C.

The star-connected PS-SCC, shown in Fig. 2(b), operates as a module-level equalizer. PS angles of all switching legs are individually manipulated to transfer power among modules depending on voltage imbalance conditions. All LC tanks are connected to the common node of X, through which any modules can transfer power directly. The detailed operation analysis for the PS-SCC will be performed in Section III.

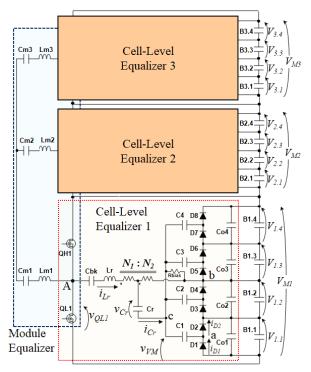

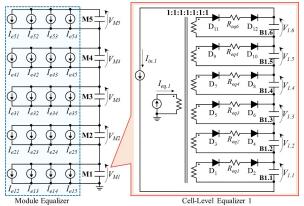

#### B. Modular Equalization System

The proposed modular equalization system for three EDLC modules, each consisting of four cells connected in series, is shown in Fig. 3. Switches are shared by TI-RVM-based celllevel equalizers and PS-SCC-based module-level equalizers. As switches are driven, both cell and module equalizers operate simultaneously. All switches are driven with a fixed duty cycle of 0.5, and all cell voltages are automatically balanced by celllevel equalizers. Meanwhile, PS angles of switching legs need to be properly manipulated to balance module voltages depending on module voltage imbalance. The control strategy will be discussed in Section IV.

#### C. Features

In comparison with the conventional modular system having a cell- and module-level equalizers separately (Fig. 1), the total switch count can be halved thanks to the integration of switches, achieving the simplified circuit.

The TI-RVM can be applied to any number of cells by adjusting the configuration of the voltage multiplier. The module count in the proposed modular equalization system can be arbitrarily extended with simply adding LC tanks in the

Fig. 3. Proposed modular equalization system with PS-SCC-based module equalizer and TI-RVM-based cell equalizer.

module-level equalizer. The voltage stresses of switches are equal to a module voltage  $(V_M)$  and are independent on module numbers. Hence, the system can be scaled up without increasing the switch voltage stress.

Since EDLCs are a voltage source, currents in equalizers must be properly limited in order to protect the circuits. Both the TI-RVM and PS-SCC exhibit inherent constant current characteristics even with open-loop control. Hence, currents in equalizers can be limited below desired levels even when voltages are severely mismatched, offering intrinsic tolerance against excessive currents.

The reliability of the proposed equalization system is considered superior to conventional ones, thanks to the reduced switch count. In general, reliability is closely dependent on circuit component counts. Reducing the switch count is the most effective way to reduce the total component count in switching power converters because each switch requires numerous auxiliary circuit components, including a gate driver IC and its power supply. The inherent constant current characteristics of the TI-RVM and PS-SCC are also the prominent feature that improves the reliability—this feature realizes an intrinsic tolerance against excessive currents without employing any protection circuits nor current sensors.

The direct power transfer among modules is also an advantage over conventional systems. Since the module-level equalizer, the star-connected PS-SCC, can directly transfer power through the common node, module voltages can be equalized faster and more efficiently than the conventional systems.

#### III. **OPERATION ANALYSIS**

Although the TI-RVM and PS-SCC are integrated with sharing switches in the proposed equalization system, these two kinds of equalizers can be analyzed separately. To simplify the analysis, all the circuit elements are assumed ideal unless otherwise noted.

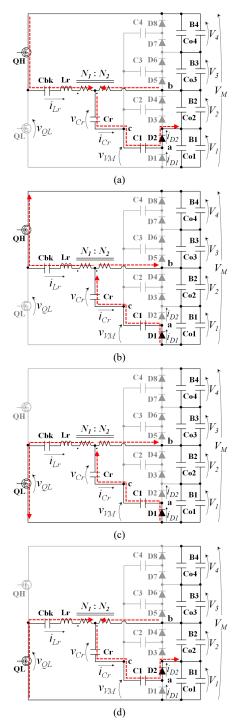

#### A. Operation Modes of TI-RVM

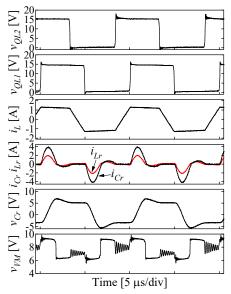

The theoretical operation waveforms and operation modes are shown in Figs. 4 and 5, respectively. High- and low-side switches, Q<sub>H</sub> and Q<sub>L</sub>, operate with a fixed duty cycle of 0.5 in a complementary mode. Current flow paths vary depending on voltage imbalance conditions. In the following, the voltage imbalance condition where B<sub>1</sub> is the least charged cell with the lowest voltage in the module is analyzed as a representative case, but operations under other imbalanced conditions can be analyzed similarly.

The switching and resonant frequencies,  $f_s$  and  $f_r$ , need to be determined so that one switching cycle contains two resonant periods, as

$$f_r > 2f_s \tag{1}$$

where

$$f_r$$

is given by

$$f_r = \frac{1}{2\pi\sqrt{\frac{L_r}{(N+1)^2}}C_r}$$

(2)

Fig. 4. Theoretical waveforms of TI-RVM when  $V_I$  is the lowest.

where  $L_r$  is the resonant inductance,  $C_r$  is the resonant capacitance, and  $N (= N_1/N_2)$  is the turn ratio of the TI.

Depending on the current flow direction of  $C_r$ ,  $i_{Cr}$ , the operation can be divided into six modes.

Mode 1 ( $0 < t \le T_r/2$ ) [Fig. 5(a )]:  $Q_H$  is turned on, and the voltage of  $Q_L$ ,  $v_{QL}$ , becomes as high as the module voltage of  $V_M$ . An input current, or a current of  $Q_H$ , is supplied by the module consisting of series-connected cells  $B_1-B_4$ . Sinusoidal resonant current  $i_{Cr}$  flows toward the voltage multiplier (VM). The high-side diode  $D_2$ , which is connected to the least charge cell  $B_1$ , conducts, and the input voltage of the VM,  $v_{VM}$ , is at a high level. This mode lasts until  $i_{Cr}$  reaches zero.

Mode 2  $(T_r/2 < t \le T_r)$  [Fig. 5(b)]: Q<sub>H</sub> is still conducting, but current flow directions are opposite to those in Mode 1. The low-side diode D<sub>1</sub> starts conducting as the direction of  $i_{Cr}$  is reversed, and  $v_{VM}$  drops to the low level. When  $i_{Cr}$  reaches zero again, this mode ends.

Mode 3 ( $T_r < t \le T_s/2$ ) [not shown]: This mode is unique to the discontinuous conduction mode. No current flows in the TI-RVM, except for smoothing capacitors.

Mode 4  $[T_s/2 < t \le (T_r + T_s)/2]$  [Fig. 5(c)]: Q<sub>L</sub> is turned on, and its voltage  $v_{QL}$  becomes zero. Current flow directions of the resonant tank and VM are identical to those in Mode 2. This mode ends as the direction of  $i_{Cr}$  is reversed.

Mode 5  $[(T_r + T_s)/2 < t \le (T_r + T_s/2)]$  [Fig. 5(d)]: Q<sub>L</sub> is still conducting, but current flow directions are opposite to those in Mode 4.

Mode 6  $[(T_r + T_s/2) < t \le T_s]$  [not shown]: Similar to Mode 3, no current flows in the entire circuit, except for smoothing capacitors.

In summary,  $D_1$  and  $D_2$  that are connected to the least charged cell  $B_1$  conduct, whereas other diodes do not. An average current flowing toward  $B_1$  is equal to that of  $D_1$  or  $D_2$  because an average current of  $C_1$  must be zero under steady-state conditions. Hence,  $B_1$  receives an equalization current from the TI-RVM, while other cells discharge to the input of the TI-RVM-based cell equalizer. Based on this operation, the

Fig. 5. Current flow paths of TI-RVM in (a) Mode 1, (b) Mode 2, (c) Mode 4, and (d) Mode 5.

voltage of  $B_1$ ,  $V_I$ , increases by receiving the equalization current, while other cell voltages  $V_2$ – $V_4$  decrease by supplying the input current for the TI-RVM. This power redistribution eventually unifies all the cell voltages. The detailed voltage equalization mechanism by the VM can be found elsewhere [15]–[17].

#### B. Operation Condition of TI-RVM

The average voltage at the node a [see Figs. 2(a) and 5] is  $V_1/2$  because conduction periods of  $D_1$  and  $D_2$  are identical. Meanwhile, the average voltage at node c is equal to that of node b (i.e.,  $V_1 + V_2$ ) due to  $R_{\text{bias}}$  [see Fig. 2(a)]. Hence, the voltage of  $C_1$  is expressed as

$$V_{C1} = V_{bias} - \frac{1}{2}V_1 \tag{3}$$

where  $V_{bias}$  is the voltage at node b (i.e.,  $V_{bias} = V_1 + V_2$ ).

From the current flow directions in Fig. 5,  $v_{VM}$  at its highand low-levels are expressed as

$$v_{VM} = \begin{cases} V_{C1} + V_1 + V_f = V_{bias} + \frac{V_1}{2} + V_f (Mode\ 1, 5) \\ V_{C1} - V_f = V_{bias} - \frac{V_1}{2} - V_f (Mode\ 2, 4) \end{cases}$$

(4)

where  $V_f$  is the forward voltage drop of diodes. This equation can be generalized as

$$v_{VM} = \begin{cases} V_{bias} + \frac{V_i}{2} + V_f (Mode \ 1, 5) \\ V_{bias} - \frac{V_i}{2} - V_f (Mode \ 2, 4) \end{cases}$$

(5)

where  $V_i$  (i = 1...n, where n is the number of cells in a module) is the voltage of the least charged cell in a module.

As mentioned in Section II-A, the VM is driven by the square wave voltage generated across  $N_2$ . In order for the VM to operate, the peak-to-peak voltage across  $N_2$  must be greater than that of  $v_{VM}$ . The peak-to-peak voltage of  $v_{VM}$ ,  $V_{VM,pp}$  can be obtained from (5), as

$$V_{VM.pp} = V_i + 2V_f \tag{6}$$

For the TI-RVM to operate, the following condition must be satisfied

$$\frac{1}{N+1}V_M > V_{VM,pp} = V_i + 2V_f \tag{7}$$

The left-hand side of the inequality represents the peak-to-peak voltage across  $N_2$ . This equation suggests that N needs to be determined by taking into account the relationship between  $V_M$  and  $V_i$ .

#### C. Modeling of TI-RVM

As can be seen in Fig. 4,  $i_{Cr}$  in Modes 1 and 2 are symmetric to that in Modes 4 and 5, respectively.  $i_{Cr}$  in each mode can be expressed as

$$\begin{cases} i_{Cr1} = -i_{Cr4} = \frac{V_M + (N+1)V_i e^{-\gamma \frac{Tr}{2}}}{Z_0(N+1)(1+e^{-\gamma T_r})} e^{-\gamma t} sin\omega_r t \\ i_{Cr2} = -i_{Cr5} = \frac{(N+1)V_i - V_M e^{-\gamma \frac{Tr}{2}}}{Z_0(N+1)(1+e^{-\gamma T_r})} e^{-\gamma t} sin\omega_r t \end{cases}$$

(8)

where  $i_{Crx}$  is  $i_{Cr}$  in Mode x (x = 1, 2, 4, 5),  $T_r$  is the resonant period,  $Z_0$  is the characteristic impedance,  $\gamma$  is the damping factor, and  $\omega_r$  is the resonant angular frequency that are given by

$$Z_0 = \sqrt{\frac{L_r}{C_r(N+1)^2}}, \quad \gamma = \frac{(N+1)^2 R}{2L_r}$$

(9)

Fig. 6. DC equivalent circuit of TI-RVM [15].

$$\omega_r = \sqrt{\frac{(N+1)^2}{L_r C_r} - \gamma^2}$$

where R is the total resistance in the resonant current path.

Since an average current of  $C_1$  must be zero under steadystate conditions, an equalization current supplied to  $B_1$  is equal to an average current of  $D_1$  or  $D_2$ . The current of  $D_1$ ,  $i_{DI}$ , in Modes 1 and 5 is equal to  $i_{Cr}$ , and therefore, the equalization current,  $I_{eq}$ , is expressed as

$$I_{eq} = \frac{1}{T_s} \left( \int_0^{\frac{T_r}{2}} i_{Cr1} dt + \int_0^{\frac{T_r}{2}} i_{Cr5} dt \right)$$

$$= \frac{\omega_s \omega_r}{2\pi Z_0 (N+1)(1+e^{-\gamma T_r})(\omega_r^2 + \gamma^2)}$$

$$\times \left\{ \left( e^{-\gamma \frac{T_r}{2}} + 1 \right)^2 V_M + (N+1)(e^{-\gamma T_r} - 1) V_i \right\}$$

(10)

where  $\omega_s$  is the angular switching frequency. By assuming *R* is ideally small and  $\gamma = 0$ , (10) can be simplified to be

$$I_{eq} \approx \frac{\omega_s}{\pi Z_0 \omega_r (N+1)} V_M \tag{11}$$

This equation suggests that  $I_{eq}$  is independent of cell voltages and can ideally be constant at a given  $V_M$ .

An average input current  $I_{in}$ , which corresponds to an average current of  $Q_H$ , is expressed as

$$I_{in} = \frac{1}{T_s} \left( \int_0^{\frac{T_r}{2}} \frac{i_{Cr1}}{N+1} dt + \int_0^{\frac{T_r}{2}} \frac{i_{Cr2}}{N+1} dt \right)$$

$$= \frac{\omega_s \omega_r \left( e^{-\gamma \frac{T_r}{2}} + 1 \right)}{2\pi Z_0 (N+1)^2 (1 + e^{-\gamma T_r}) (\omega_r^2 + \gamma^2)}$$

$$\times \left\{ \left( 1 - e^{-\gamma \frac{T_r}{2}} \right)^2 V_M + (N+1) (1 + e^{-\gamma T_r}) V_i \right\}$$

(12)

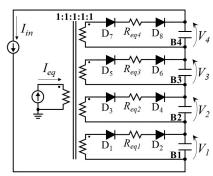

In the previous work, a dc equivalent circuit of a VM-based cell voltage equalizer has been derived [15]. The TI-RVM can also be expressed in the identical equivalent circuit, though its current characteristics are totally different. The dc equivalent circuit of the TI-RVM is shown in Fig. 6. All cells supply an input current in the form of  $I_{in}$  for the input, whereas an equalization current  $I_{eq}$  is redistributed to cells through an ideal multi-winding transformer. Since all cells are connected to the multi-winding transformer through an equivalent resistor  $R_{eqi}$  and two diodes,  $I_{eq}$  automatically flows toward the least charged cell(s) having the lowest voltage in the module. Characteristics

of the current sources of  $I_{eq}$  and  $I_{in}$  correspond to (10) and (12), respectively, while  $R_{eqi}$  is given by [23]

$$R_{eqi} = \frac{1}{2C_i f_s} + \frac{2f_r}{f_s} r$$

(13)

where  $C_i$  is the capacitance of  $C_i$ , and r is the collective resistance of the current path of the TI-RVM.

#### D. Transformation from Star- to Δ-Connected PS-SCCs

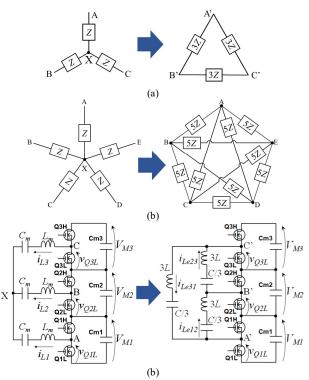

Each LC tank in the star-connected PS-SCC, shown in Fig. 2(b), is connected between each node and the common node X, and therefore, operations of three LC tanks are mutually dependent. For example, the voltage across the LC tank tied to node A is dependent on the voltages at both nodes B and C (i.e.,  $v_{Q2L}$  and  $v_{Q3L}$ ). It implies that currents of LC tanks,  $i_{LI}$ – $i_{L3}$ , are dependent on all node voltages,  $v_{QLI}$ – $v_{QL3}$ , making the analysis complex. The degree of complexity soars as the number of LC tanks or modules grows, rendering the analysis impractical. In this section, the star-connected PS-SCC is transformed into a  $\Delta$ -connected circuit in order to simplify the analysis.

In general, a star-connected or Y-connected circuit can be transformed into a  $\Delta$ -connected one, as shown in Fig. 7(a). Branch impedances Z in the star-connected circuit containing three input nodes  $\Delta$ -C are equivalently transformed to be 3Z in the  $\Delta$ -connected circuit. For the case of k branches, the transformed equivalent impedance will be k times that of the original impedance Z. The case of k = 5, for example, is shown in Fig. 7(b), in which all nodes are individually connected through an equivalent impedance of 5Z.

Fig. 7. Transformation from star- to  $\Delta$ -connected circuits. (a) Three impedance branches. (b) Five impedance branches. (b) PS-SCC for three modules.

LC tanks in the star-connected PS-SCC can similarly be transformed into the  $\Delta$ -connected version, as shown in Fig. 7(c), in which the PS-SCC for three modules is illustrated as a representative case. The inductance  $L_m$  and capacitance  $C_m$  in the star-connected PS-SCC for three modules are transformed to be  $3L_m$  and  $1/3C_m$  in the  $\Delta$ -connected PS-SCC. Each LC tank in the  $\Delta$ -connected PS-SCC is directly connected between two out of three nodes A'-C', and therefore, currents of the LC tanks ( $i_{Le12}$ ,  $i_{Le23}$ , and  $i_{Le31}$ ) can be determined in a similar way as a basic PS-SCC [49]. Although the PS-SCC for three modules (i.e., k = 3) only is illustrated as a representative case, the transformation from the star- to  $\Delta$ -connected PS-SCC can be applied to any integer value of k.

#### E. Modeling of Basic PS-SCC

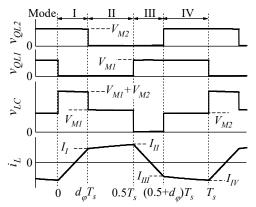

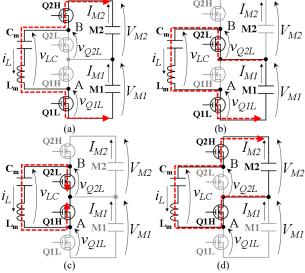

This subsection presents the theoretical model of the basic PS-SCC for two modules. Operation waveforms and current flow paths in the case of  $V_{MI} > V_{M2}$  (power transfer from  $M_1$  to  $M_2$ ) are shown in Figs. 8 and 9, respectively. The operation is roughly divided into four modes, Modes I–IV. Dead time

Fig. 8. Theoretical waveforms of PS-SCC in the case of  $V_{MI} > V_{M2}$

Fig. 9. Current flow paths in PS-SCC in (a) Mode I, (b) Mode II, (c) Mode III, and (d) Mode IV.

periods are omitted to save page length.

Mode I  $(0 < t \le d_{\varphi}T_s)$  [Fig. 9(a)]: Q<sub>1L</sub> and Q<sub>2H</sub> are turned on. The voltage applied to the LC tank,  $v_{LC}$ , is equal to  $V_{MI} + V_{M2}$ . The LC tank stores the energy as its current  $i_L$  increases.

Mode II  $(d_{\varphi}T_s < t \le 0.5T_s)$  [Fig. 9(b)]: Q<sub>2L</sub> and Q<sub>2H</sub> are turned on and off, respectively, and the LC tank is charged by M<sub>1</sub>.  $v_{LC}$  is equal to  $V_{MI}$ , and the increase rate of  $i_L$  becomes gentler than that in Mode I.

Mode III  $[0.5T_s < t \le (0.5 + d_{\varphi})T_s]$  [Fig. 9(c)]: Q<sub>1H</sub> is turned on, and the LC tank is short-circuited.  $i_L$  steeply decreases, and its polarity is reversed.

Mode IV  $[(0.5 + d_{\varphi})T_s < t \le T_s]$  [Fig. 9(d)]: Q<sub>2L</sub> and Q<sub>2H</sub> are turned off and on, respectively.  $v_{LC}$  is equal to  $V_{M2}$ , and the LC tank discharges to M<sub>2</sub>.

$i_L$  at the end of Modes I–IV,  $I_L$ – $I_{IV}$ , are expressed as

$$\begin{cases} I_{I} = -I_{III} = \frac{1}{8f_{s}L} \{V_{M2} + (4d_{\varphi} - 1)V_{M1}\} \\ I_{II} = -I_{IV} = \frac{1}{8f_{s}L} \{V_{M1} + (4d_{\varphi} - 1)V_{M2}\} \end{cases}$$

(14)

where  $d_{\varphi}$  (=  $\varphi/\pi$ ) is the PS duty cycle. Average currents of M<sub>1</sub> and M<sub>2</sub>,  $I_{MI}$  and  $I_{M2}$ , are yielded as

$$\begin{cases} I_{M1} = \frac{d_{\varphi}(1 - 2|d_{\varphi}|)}{4f_{s}L} V_{M2} \\ I_{M2} = \frac{-d_{\varphi}(1 - 2|d_{\varphi}|)}{4f_{s}L} V_{M1} \end{cases}$$

(15)

This equation dictates the current relationship between adjacent two modules. Accordingly, a dc equivalent circuit of the basic PS-SCC can be obtained as shown in Fig. 10(a).

#### F. Modeling of ∆-Connected PS-SCC

The  $\Delta$ -connected PS-SCC, shown in Fig. 7(c), consists of three basic PS-SCCs. Hence, a dc equivalent circuit of the  $\Delta$ -connected PS-SCC is an extended version of the basic topology, as shown in Fig. 10(b). From this dc equivalent circuit, average currents of Modules  $M_1$ – $M_3$ ,  $I_{MJ}$ – $I_{M3}$ , are given by

$$\begin{cases} I_{M1} = I_{e12} + I_{e13} \\ I_{M2} = I_{e21} + I_{e23} \\ I_{M3} = I_{e31} + I_{e32} \end{cases}$$

(16)

In a system consisting of m modules, a current of i-th module  $M_i$  (i = 1...m),  $I_{Mi}$ , can be generalized as

Fig. 10. DC equivalent circuit of (a) basic PS-SCC and (b)  $\Delta$ -connected PS-SCC for three modules.

$$I_{Mi} = \sum_{i=1}^{m} I_{eij} \tag{17}$$

where  $I_{eij}$  is an average current flowing from j-th module  $M_j$  to  $M_i$ . According to (15),  $I_{eij}$  is generalized as

$$I_{eij} = \frac{d_{\varphi ij} \left(1 - 2\left|d_{\varphi ij}\right|\right)}{4mf_s L} V_{Mj} \tag{18}$$

where  $d_{\varphi ij}$  is the PS duty cycle between  $M_i$  and  $M_j$  with respect to  $M_i$  (i.e.,  $d_{\varphi ij} = d_{\varphi i} - d_{\varphi j} = -d_{\varphi ji}$ ).

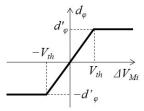

### IV. CONTROL STRATEGY FOR STAR-CONNECTED PS-SCC

The TI-RVM is a unidirectional converter with an inherent constant current characteristic (see Section III-C), and all cell voltages in each module are automatically equalized without feedback control. Meanwhile, the PS-SCC is a bidirectional converter, and its power flow needs to be controlled based on voltage imbalance conditions.

$d_{\varphi}$  for the proposed PS-SCC is determined based on  $\Delta V_{Mi}$ , the voltage difference between the average module voltage  $V_{M.ave}$  and individual module voltage  $V_{Mi}$ .

$$\Delta V_{Mi} = V_{M.ave} - V_{Mi} \tag{19}$$

$d_{\varphi}$  for M<sub>i</sub>,  $d_{\varphi_i}$ , is determined to obey the following condition (see Fig. 11)

$$d_{\varphi i} = \begin{cases} d'_{\varphi} & (V_{th} < \Delta V_{Mi}) \\ \frac{d'_{\varphi}}{V_{th}} \Delta V_{Mi} & (-V_{th} \le \Delta V_{Mi} \le V_{th}) \\ -d'_{\varphi} & (\Delta V_{Mi} < V_{th}) \end{cases}$$

(20)

where  $V_{th}$  is the threshold voltage. When  $\Delta V_{Mi}$  is beyond  $\pm V_{th}$  and module voltages are imbalanced,  $d_{\varphi i}$  is fixed to be  $\pm d'_{\varphi}$  so that currents among modules can be a constant value [see (18)].

#### V. DESIGN EXAMPLE

As mentioned in Section I, the module voltages in practical use would be more prone to be imbalanced than cell voltages because the larger geometries of modules lead to larger temperature mismatch. Given this situation, the module-level equalizers are designed capable of a larger equalization current than cell-level equalizers in this section.

#### A. Granularity Level

There is no clear guideline on the optimal granularity level the system is divided into modules, but the number of cells in each module should be determined based on a tradeoff between the switch count and voltage stresses of circuit elements.

Fig. 11. Relationship between phase-shift duty cycle  $d_{\varphi}$  and voltage difference  $\Delta V_{Mi}$ .

The coarser the granularity level, the less will be the switch count. However, voltage stresses of circuit components are prone to soar because the number of cells as well as the module voltage increases as the granularity level becomes coarse. It is recommended to determine the granularity level based on the acceptable voltage stresses of circuit elements.

For example, outer coupling capacitors,  $C_1$  and  $C_n$  (n being the number of cells in each module), are exposed to the highest voltage stress in each module, and their stresses are approximately  $0.5n \times V_{cell}$ . The voltage stresses of switches are equal to the module voltage of  $V_M$  (=  $n \times V_{cell}$ ). Modules containing a moderate number of cells allow low-voltage circuit components to be used. Modules comprising less than twelve cells connected in series, for example, allow 25-V ceramic capacitors and 100-V MOSFETs to be used.

#### B. Cell-Level Equalizer (TI-RVM)

The design target is an EDLC-based energy storage system consisting of five modules (m = 5), each containing six cells (n = 6). Component values of the TI-RVM are determined so that  $I_{eq} = 0.6$  A at  $V_M = 15$  V and  $f_s = 100$  kHz. Given the component availability, a TI with N = 1.0 is selected.

$I_{eq}$  is expressed by (10), but the damping factor  $\gamma$  is unknown at the design stage. Assuming  $\gamma = 0$ , component values are determined using (11) with anticipating 10–15% decrease in  $I_{eq}$  due to the neglected  $\gamma$ . Substituting  $I_{eq} = 0.7$  A ( $\approx 0.6$  A/1.15) into (11) yields

$$\frac{1}{Z_0 \omega_r} = C_r = 467 \times 10^{-9} \to C_r = 470 \text{ nF}$$

(21)

According to (1), the resonant frequency  $f_r$  must be greater than twice the switching frequency  $f_s$ . Given the component tolerance and ageing over time,  $L_r$  is determined from (9) with applying  $f_r > 3f_s$ , as

$$L_r < 2.4 \times 10^{-6} \rightarrow L_r = 2.1 \,\mu\text{H}$$

(22)

The resonant operation, as well as  $I_{eq}$  of the TI-RVM, is sensitive to capacitance in the resonant current path. Coupling capacitors  $C_i$  (i = 1...6) is connected in series with  $C_r$ , as shown in Fig. 5. Hence, the capacitance of coupling capacitors  $C_i$  should be determined so that  $C_i$  has no influence on  $I_{eq}$ . To this end,  $C_i$  must be rather larger than  $C_r$ , and is determined to be

Fig. 12. DC equivalent circuit of modular equalization system for five EDLC modules, each consisting of six cells.

100 times greater than  $C_r$  (i.e.,  $C_i = 47 \mu F$ ).

#### C. Module-Level Equalizer (PS-SCC)

The design target is  $I_{Mi} = 1.0$  A at  $V_M = 15$  V and  $\varphi = 45^{\circ}$  (or  $(d_{\varphi} = 0.25)$ . Substituting m = 5 into (17) and (18) yields

$$L_m = 46.9 \times 10^{-6} \rightarrow L_m = 47 \,\mu\text{H}$$

(23)

The capacitance of  $C_m$  needs to be determined so that the resonance between  $L_m$  and  $C_m$  has little impact on the operation of the PS-SCC. An LC tank with a resonant frequency one-tenth of  $f_s$  is sufficient;

$$\frac{1}{2\pi\sqrt{L_mC_m}} \approx \frac{f_s}{10} \tag{24}$$

Substituting  $L_m = 47 \mu H$  into (24) yields

$$C_m = 53.9 \times 10^{-6} \to C_m = 47 \,\mu\text{F}$$

(25)

## VI. EQUALIZATION SIMULATION BASED ON DC EQUIVALENT CIRCUIT

In Section IV, dc equivalent circuits of the TI-RVM and PS-SCC were derived, as shown in Figs. 6 and 10. Based on the combination of these two equivalent circuits, a dc equivalent circuit of the proposed modular equalization system as a whole can be obtained, as shown in Fig. 12. This figure illustrates the system having five modules  $M_1$ – $M_5$  in series, each comprising six cells. It should be noted that the equivalent circuit for the cell-level equalizer (or TI-RVM) for  $M_1$  only is depicted in the inset while others are not shown for the sake of clarity.

In general, equalization processes take a long stretch of time ranging from several ten minutes to hours or even days whereas equalizers operate at a frequency higher than several ten kilohertz. In other words, simulation-based equalization tests

Fig. 13. Simulated equalization profiles of module voltages and cell voltages in each module.

using an actual circuit (e.g., Fig. 3) will result in impractically huge simulation burden and time. The derived dc equivalent circuit, on the other hand, does not contain switching devices operating at a high frequency, and therefore simulation burden and time can be drastically reduced.

An equalization test based on the dc equivalent circuit shown in Fig. 12 was performed using PSIM software. Component values used for the prototype (see Table I in Section VII) were applied, and values of  $R_{eqi}$  were determined to be 2.478  $\Omega$  at  $f_s$  = 100 kHz and  $f_r$  = 248 kHz. Current sources of  $I_{eq}$ ,  $I_{in}$ , and  $I_{eij}$  were modeled using simplified C-blocks to obey (10), (12), and (18), respectively.  $V_{th}$  and  $d'_{\varphi}$  were set to be 0.5 V and 0.125, respectively.

The resultant equalization profiles are shown in Fig. 13. At the beginning of the equalization,  $V_{MI}$  and  $V_{M2}$  were lower than the average module voltage, and therefore,  $d_{\varphi I}$  and  $d_{\varphi 2}$  were clumped to be -0.125. Meanwhile,  $d_{\varphi 3}-d_{\varphi 5}$  were clumped to be 0.125 as  $V_{M3}-V_{M5}$  were higher than the average module voltage. Thanks to the constant current characteristics of the PS-SCC [see (18)], module voltages,  $V_{MI}-V_{M5}$ , linearly changed and converged to 9.0 V.

On the other hand, cell voltages in each module exhibited different tendencies because cells were equalized by TI-RVMs while module voltages were also changing at the same time. In  $M_1$ , for example, all of  $V_{I.I}$ – $V_{I.6}$  increased as  $V_{MI}$  increased due to the module-level equalization by the PS-SCC, while cell voltage imbalance in  $M_1$  gradually disappeared thanks to the cell-level equalization by the TI-RVM. Cell voltages in each module were gradually equalized by the energy redistribution through TI-RVMs, and all cell voltages were eventually unified

Fig. 14. Photographs of EDLC module comprising six cells.

Table I

COMPONENT LIST

| COMPONENT LIST                  |                                                        |  |  |  |  |  |  |  |

|---------------------------------|--------------------------------------------------------|--|--|--|--|--|--|--|

| Component                       | Value                                                  |  |  |  |  |  |  |  |

| Q <sub>H</sub> , Q <sub>L</sub> | Dual MOSFET, IRF7341, $R_{on} = 50 \text{ m}\Omega$    |  |  |  |  |  |  |  |

| Tapped                          | MSD1514-273MEB, $N_1:N_2=1:1$                          |  |  |  |  |  |  |  |

| Inductor                        | $L_{kg} = 1.0 \mu H, L_{mg} = 27.2 \mu H$              |  |  |  |  |  |  |  |

| $L_{r}$                         | 2.1 μΗ                                                 |  |  |  |  |  |  |  |

| $C_{bk}$                        | Ceramic Capacitor, 9.4 µF                              |  |  |  |  |  |  |  |

| $C_{r}$                         | Film Capacitor, 470 nF                                 |  |  |  |  |  |  |  |

| $C_1 - C_6$                     | Ceramic Capacitor, 47 μF                               |  |  |  |  |  |  |  |

| Diode                           | Schottky Barrier Diode, RB496EA, $V_f = 0.4 \text{ V}$ |  |  |  |  |  |  |  |

| Co1-Co6                         | Ceramic Capacitor, 660 μF                              |  |  |  |  |  |  |  |

| $L_{m1}-L_{m3}$                 | 4.7 μΗ                                                 |  |  |  |  |  |  |  |

| $C_{m1}$ - $C_{m3}$             | Ceramic Capacitor, 47 μF                               |  |  |  |  |  |  |  |

| Gate Driver                     | IRS2184S                                               |  |  |  |  |  |  |  |

to be 1.5 V.

#### VII. EXPERIMENTAL RESULTS

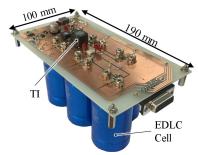

#### A. Prototype

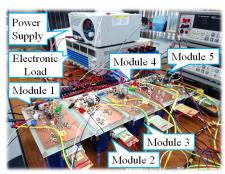

Many of EDLC manufactures provide six-cell modules that can be an alternative to traditional 12-V lead-acid batteries [50],[51]. We built six-cell modules consisting of the TI-RVM-based cell-level equalizer and an LC tank, as shown in Fig. 14. Six cells, each with a capacitance of 400 F at a rated charge voltage of 2.5 V, were mounted on the printed circuit board. The components used for the prototype are listed in Table I. The resonant frequency  $f_r$  was 264 kHz, and the prototype was operated at a switching frequency  $f_s$  of 100 kHz to satisfy (1). TMS230F28335 control card (Texas Instruments) was used to generate gating signals for MOSFETs.

#### B. Operation Waveforms

Key Operation waveforms of the equalization system for two modules were measured using the experimental setup shown in Fig. 15(a). All cells were removed, and a variable resistor  $R_{\text{var}}$  and an external power supply  $V_{\text{ext}}$  were connected instead of modules.

Measured key operation waveforms are shown in Fig. 16. Although oscillations due to parasitic capacitances of MOSFETs and Schottky barrier diodes were observed, these waveforms matched very well with the theoretical ones in Figs. 4 and 8, verifying the fundamental operation.

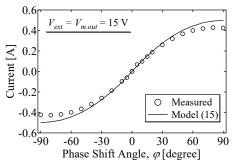

#### C. Characteristics of PS-SCC

Current characteristics of the PS-SCC were measured using the experimental setup shown in Fig. 15(a). Points Z were broken so that TI-RVMs did not operate. The current

Fig. 15. Experimental setup to measure characteristics of (a) PS-SCC and (b) TI-RVM.

Fig. 16. Measured key waveforms.

Fig. 17. Measured current characteristic of PS-SCC.

characteristic as a function of  $\varphi$  for  $V_{m.out} = 15$  V was measured, as shown in Fig. 17. The experimental and theoretical characteristics of (15) matched very well.

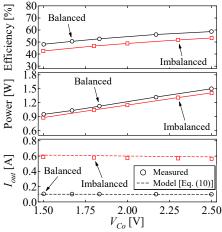

The measured currents  $I_{m.out}$  and power conversion efficiencies as a function of output voltage  $V_{m.out}$  are shown in Fig. 18. The loss due to the gate driver and control circuit was excluded for the efficiency calculation.  $I_{m.out}$  slightly increased as  $V_{m.out}$  decreased, but no excessive current flowed even when  $V_{m.out}$  was zero, demonstrating its intrinsic current limitation capability. The efficiencies monotonically increased with  $V_{m.out}$ , and the peak efficiency was 90% at  $V_{m.out} = 15$  V and  $\varphi = 45^{\circ}$ .

#### D. Characteristics of TI-RVM

The experimental setup shown in Fig. 15(b) was used to measure the characteristics of the TI-RVM alone under a voltage-imbalanced and -balanced conditions. All cells were removed, and a variable resistor  $R_{var}$  was connected in parallel with  $C_{o1}$  or the series connection of  $C_{o1}$ – $C_{o6}$  through the tap X or Y, respectively. Closing the tap X and Y can emulate current flow paths under voltage-imbalanced and -balanced conditions, respectively. An external power supply with  $V_{ext} = 15$  V was connected to the input port of the switching leg.

Fig. 18. Measured characteristics of PS-SCC.

Fig. 19. Measured characteristics of TI-RVM.

Measured characteristics of the TI-RVM alone are shown in Fig. 19. The output currents,  $I_{out}$ , were constant and independent on the output voltage,  $V_{Col}$ , thus verifying the constant current characteristic. Iout under the imbalanced condition was six times greater than that under the balanced condition because the equalization current concentrated to Col. The inferior efficiencies lower than 60% were chiefly due to diode conduction losses; forward voltage drops of approximately 0.4 V (see Table I) took a significant portion of the output voltage lower than 2.5 V. However, the poor efficiency performance would not impair a system efficiency in practical use because the required power for cell-level equalization is negligibly small compared to that for charging or discharging power. In general, an equalization current for cells equivalent to onehundredth of charging or discharging current is considered sufficient to eliminate or preclude cell voltage imbalance [52]– [54].

#### E. Equalization Test

A photograph of the experimental setup for equalization tests is shown in Fig. 20. Five modules were connected using cables. Module voltages as well as all cell voltages in each module

Fig. 20. Experimental setup for equalization tests.

were severely imbalanced intentionally. The equalization test was performed under the same condition as simulation analysis  $(d'_{\varphi} = 0.125 \text{ and } V_{th} = 0.5 \text{ V}).$

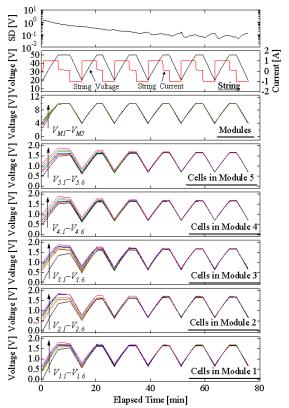

The resultant equalization profiles are shown in Fig. 21. The module voltage imbalance was quickly eliminated within 15 min, while cell voltages in each module gradually equalized. The module voltages and cell voltages were equalized at different rates. After the module voltages were balanced,  $d_{\varphi}$  was set to be 0 so that the module-level equalizers did not process power. This implies that the module-level equalizers were virtually disabled, and the system efficiency was not impaired. The standard deviation (SD) of cell voltages decreased down to as low as 27 mV at the end of the equalization test, demonstrating the equalization performance of the proposed modular equalization system. These experimental equalization profiles showed good agreement with simulation results in Fig. 13, verifying the derived mathematical model as well as the de

Fig. 21. Resultant equalization profiles of module voltages and cell voltages in each module.

equivalent circuit.

An equalization test during charge-discharge cycling was also performed. The series-connected modules were charged with a constant-current-constant-voltage charging scheme of 1.0 A-50 V (10 V/module) and were discharged with a constant current of 1.0 A. The charge-discharge cycle was repeated for six cycles. Measured cycling profiles are shown in Fig. 22. Module voltages were nearly equalized in the first cycle, and all modules were uniformly charged to 10 V without being overcharged. Meanwhile, cell voltages in each module gradually converged, and cell voltage imbalance almost disappeared in the fourth cycle. The fluctuation in SD after the fourth cycle was due to a minor mismatch in cell capacity—the mismatch in capacity naturally led to slight voltage divergence during cycling. In summary, module and cell voltages were well equalized even during cycling, demonstrating the equalization performance of the proposed modular equalization system.

## VIII. COMPARISON WITH CONVENTIONAL MODULARIZED EQUALIZERS

Component counts, efficiency, circuit complexity, cost, size, balancing speed, etc. vary depending on equalizer topologies and architectures. The circuit complexity and cost are closely relevant to the component count, especially the switch count, because each switch requires an auxiliary circuit including a gate driver IC and its power supply. The size of the equalizer is roughly dependent on the number of bulky magnetic components. Hence, the component count can be a good index

Fig. 22. Resultant equalization profiles of module voltages and cell voltages in each module during charge-discharge cycling.

Table II

COMPARISON BETWEEN PROPOSED AND CONVENTIONAL MODULARIZED EQUALIZERS

| Topology | Module Equalizer                        | Cell Equalizer                     | Switch                     | L                        | $C^{\dagger\dagger}$ | D   | Trans former                | Reported Efficiency                      |

|----------|-----------------------------------------|------------------------------------|----------------------------|--------------------------|----------------------|-----|-----------------------------|------------------------------------------|

| [25]     | Forward Converter                       | Flyback Converter                  | mn SSR <sup>†</sup><br>+ m | -                        | -                    | n   | mn + m                      | 81.6% (average)                          |

| [26]     | SCC                                     | SCC                                | 2mn + 2m                   | -                        | m(n-1) + (m-1)       | -   | -                           | -                                        |

| [26]     | SCC                                     | Multi-Winding<br>Flyback Converter | 3 <i>m</i>                 | -                        | m-1                  | mn  | m (n Secondary<br>Windings) | -                                        |

| [41]     | Multidirectional<br>Multiport Converter | PWM Converter                      | 2m(n-1) + 2m               | m (n-1)                  | 2 <i>m</i>           | -   | 1 (m Secondary<br>Windings) | 89.7% (average)                          |

| [40]     | PWM Converter                           | PWM Converter                      | 2m(n-1) + 2(m-1)           | m(n-1) + (m-1)           | -                    | -   | -                           | -                                        |

| [43]     | Flyback Converter                       | Flyback Converter                  | mn                         | -                        | -                    | -   | m (n Secondary Windings)    | 89.4% (peak)                             |

| [45]     | Forward Converter                       | Forward Converter                  | mn                         | -                        | ı                    | 1   | m (n Secondary Windings)    | 95.6% (peak)                             |

| [46]     | SCC                                     | Multi-Winding<br>Flyback Converter | mn + 2m                    | -                        | m-1                  | m   | m (n Secondary Windings)    | 83.3% (average)                          |

| [47]     | SCC                                     | IVD-VM                             | 2 <i>m</i>                 | 2 <i>m</i>               | m(n+1)<br>+(m-1)     | 2mn | -                           | Cell: 65.3% (peak)<br>Module: 96% (peak) |

| Proposed | Phase-Shift SCC                         | TI-RVM                             | 2 <i>m</i>                 | m (Inductor)<br>+ m (TI) | m (n +3)             | 2mn | -                           | Cell: 60% (peak)<br>Module: 85.6 (peak)  |

† Solid-State Relay

†† Smoothing capacitors excluded

to represent the circuit complexity, cost, and size. This section compares the proposed modular equalization system with conventional modularized equalizers from the viewpoint of component counts and reported power conversion efficiency. Balancing speed or time, on the other hand, is excluded as it cannot be fairly compared from the reported figures—various factors, such as initial voltage imbalance, number of cells in modules, equalization current, cell capacity, etc. influence balancing speeds.

Table II compares the component counts and power conversion efficiencies of the proposed and conventional modularized equalizers. m is the module count, and n is the cell count in each module. The switch counts of conventional equalizers, except for [47], are dependent on both m and n, implying that module- and cell-level equalizers are separately used and are not integrated. Many of conventional topologies rely on multi-winding transformers, with which the number of passive components can be significantly reduced. However, the design difficulty of multi-winding transformers is often cited as a top concern because of the requirement of strict parameter matching among multiple secondary windings [2]—the design difficulty significantly soars as the number of windings increases

Meanwhile, the proposed modular equalization system can minimize the switch count in addition to the lack of multiwinding transformers. Although *m* inductors and *m* TIs are necessary, these can be rather smaller than multi-winding transformers because of their simple structures. The efficiency of the module-level equalizer is comparable to that of conventional ones, whereas the power conversion efficiency of the cell-level equalizer in the proposed system is inferior. However, as discussed in Section VII-D, the poor efficiency of the cell-level equalizer would not be a serious problem as the processed power in the cell-level equalizer in practical use is even smaller than one-hundredth that of a main charger or converter [52]–[54].

#### IX. CONCLUSIONS

The modular equalization system integrating module- and cell-level equalizers has been proposed in this paper. Star-connected PS-SCCs and TI-RVMs are used as a module- and cell-level equalizers, respectively, and these are integrated with sharing switches, hence achieving reduced circuit complexity and cost by halving the total switch count. Furthermore, equalization currents in both the PS-SCC and TI-RVM can be inherently constant even when voltages are severely mismatched, offering intrinsic current limitation capability at both the module and cell levels.

Detailed operation analyses were separately performed for the TI-RVM and PS-SCC. Based on the mathematical analysis, the dc equivalent circuit of the proposed modular equalization system was derived, with which simulation burden and time can be drastically reduced thanks to the lack of switching devices operating at a high frequency. Equalization profiles of the dc equivalent circuit matched very well with the experimental results, verifying the analysis and derived equivalent circuit.

The prototype for five EDLC modules, each consisting of six cells connected in series, was built. The experimental equalization tests were performed from the voltage-imbalanced condition. Module and cell voltages were equalized at different rates, and voltage imbalance was eventually eliminated even during cycling, demonstrating the equalization performance of the proposed modular equalization system.

#### REFERENCES

- [1] J. G. Lozano, E. R. Cadaval, M. I. M. Montero, and M. A. G. Martinez, "Battery equalization active methods," *J. Power Sources*, vol. 246, pp. 934–949, 2014.

- [2] J. Cao, N. Schoffeld, and A. Emadi, "Battery balancing methods: a comprehensive review," in Proc. IEEE Veh. Power Propulsion Conf., pp. 1–6. Sep. 2008

- [3] P.A. Cassani and S.S. Williamson, "Design, testing, and validation of a simplified control scheme for a novel plug-in hybrid electric vehicle

- battery cell equalizer," *IEEE Trans. Ind. Electron.*, vol. 57, no. 12, pp. 3956–3962, Dec. 2010.

- [4] T.H. Phung, A. Collet, and J. Crebier, "An optimized topology for next-to-next balancing of series-connected lithium-ion cells," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4603–4613, Sep. 2014.

- [5] J. Ewanchuk and J. Salmon, "A modular balancing bridge for series connected voltage sources," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4712–4722, Sep. 2014.

- [6] A. Baughman and M. Ferdowsi, "Double-tiered switched-capacitor battery charge equalization technique," *IEEE Trans. Ind. Appl.*, vol. 55, no. 6, pp. 2277–2285, Jun. 2008.

- [7] M. Uno and K. Tanaka, "Influence of high-frequency charge-discharge cycling induced by cell voltage equalizers on the life performance of lithium-ion cells," *IEEE Trans. Veh. Technol.*, vol. 60, no. 4, pp. 1505– 1515, May 2011.

- [8] Y. Yuanmao, K.W.E. Cheng, and Y.P.B. Yeung, "Zero-current switching switched-capacitor zero-voltage-gap automatic equalization system for series battery string," *IEEE Trans. Power Electron.*, vol. 27, no. 7, pp. 3234–3242, Jul. 2012.

- [9] M.Y. Kim, C.H. Kim, J.H. Kim, and G.W. Moon, "A chain structure of switched capacitor for improved cell balancing speed of lithium-ion batteries," *IEEE Trans. Ind. Electron.*, vol. 61, no. 9, pp. 3989–3999, Aug. 2014.

- [10] Y. Shang, B. Xia, F. Lu, C. Zhang, N. Cui, and C.C. Mi, "A switched-coupling-capacitor equalizer for series-connected battery strings," *IEEE Trans. Power Electron.*, vol. 32, no. 10, pp. 7694–7706, Oct. 2017.

- [11] Y. Shang, Q. Zhang, N. Cui, and C. Zhang, "A cell-to-cell equalizer based on three-resonant-state switched-capacitor converters for seriesconnected battery strings," *Energies*, vol.10, no. 206, 2017.

- [12] N. H. Kutkut, D. M. Divan, and D. W. Novotny, "Charge equalization for series connected battery strings," *IEEE Trans. Ind. Appl.*, vol. 31, no. 3, pp. 562–568, May/Jun. 1995.

- [13] M. Uno and K. Tanaka, "Single-switch cell voltage equalizer using multistacked buck-boost converters operating in discontinuous conduction mode for series-connected energy storage cells," *IEEE Trans.* Veh. Technol., vol. 60, no. 8, pp. 3635–3645, Oct. 2011.

- [14] M. Uno and K. Tanaka, "Double-switch single-transformer cell voltage equalizer using a half-bridge inverter and voltage multiplier for seriesconnected supercapacitors," *IEEE Trans. Veh. Technol.*, vol. 61, no. 9, pp. 3920–3930, Nov. 2012.

- [15] M. Uno and K. Tanaka, "Single-switch multioutput charger using voltage multiplier for series-connected lithium-ion battery/supercapacitor equalization," *IEEE Trans. Ind. Electron.*, vol. 60, no. 8, pp. 3227–3239, Aug. 2013.

- [16] M. Uno and A. Kukita, "Double-switch equalizer using parallel- or seriesparallel-resonant inverter and voltage multiplier for series-connected supercapacitors," *IEEE Trans. Power Electron.*, vol. 29, no. 2, pp. 812– 828. Feb. 2014.

- [17] M. Uno and A. Kukita, "Single-switch single-transformer cell voltage equalizer based on forward-flyback resonant inverter and voltage multiplier for series-connected energy storage cells," *IEEE Trans. Veh. Technol.*, vol. 63, no. 9, pp. 4232–4247, Nov. 2014.

- [18] M. Arias, J. Sebastian, M.M. Hernando, U. Viscarret, and I. Gil, "Practical application of the wave-trap concept in battery-cell equalizers," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5616–5631, Oct. 2015.

- [19] M. Uno and A. Kukita, "String-to-battery voltage equalizer based on half-bridge converter with multi-stacked current doublers for series-connected batteries," *IEEE Trans. Power Electron.*, vol. 34, no. 2, pp. 1286–1298, Feb. 2019.

- [20] A. Xu, S. Xie, and X. Liu, "Dynamic voltage equalization for seriesconnected ultracapacitors in EV/HEV applications," *IEEE Trans. Veh. Technol.*, vol. 58, no. 8, pp. 3981–3987, Oct. 2009.

- [21] S. Li, C.C. Mi, and M. Zhang, "A high-efficiency active battery-balancing circuit using multiwinding transformer," *IEEE Trans. Ind. Appl.*, vol. 49, no. 1, pp. 198–3207, Jan./Feb. 2013.

- [22] C.C. Hua, Y.H. Fang, Y.L. Chen, "Modified rectifications for improving the charge equalisation performance of series-connected battery stack," *IET Trans. Power Electron.*, vol. 9, no. 9, pp. 1924–1932, 2016.

- [23] M. Uno and K. Kukita, "Bidirectional PWM converter integrating cell voltage equalizer using series-resonant voltage multiplier for seriesconnected energy storage cells," *IEEE Trans. Power Electron.*, vol. 30, no. 6, pp. 3077–3090, Jun. 2015.

- [24] K. Yashiro and M. Uno, "Transformer-less bidirectional PWM converter integrating voltage multiplier-based cell voltage equalizer for seriesconnected electric double-layer capacitors," *IEEE Trans. Power Electron.*, vol. 34, no. 5, pp. 4304–315, May 2019.

- [25] H.S. Park, C.E. Kim, C.H. Kim, G.W. Moon, and J.H. Lee, "A modularized charge equalizer for an HEV lithium-ion battery string," *IEEE Trans. Ind. Electron.*, vol. 56, no. 5, pp. 1464–1476, May 2009.

- [26] H.S. Park, C.H. Kim, K.B. Park, G.W. Moon, and J.H. Lee, "Design of a charge equalizer based on battery modularization," *IEEE Trans. Veh. Technol.*, vol. 58, no. 7, pp. 3216–3223, Sep. 2009.

- [27] C.H. Kim, M.Y. Kim, H.S. Park, and G.W. Moon, "A modularized two-stage charge equalizer with cell selection switches for series-connected lithium-ion battery string in a HEV," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3764–3774, Aug. 2012.

- [28] A. M. Imtiaz, F. H. Khan, and H. Kamath, "Time shared flyback converter" based regenerative cell balancing technique for series connected Li-ion battery strings," *IEEE Trans. Power Electron.*, vol. 28, no. 12, pp. 5960– 5975, Dec. 2013.

- [29] S. Yarlagadda, T. T. Hartley, and I. Husain, "A battery management system using an active charge equalization technique based on a DC/DC converter topology," *IEEE Trans. Ind. Appl.*, vol. 49, no. 6, pp. 2720– 2729, Nov./Dec. 2013.

- [30] Y. Shang, C. Zhang, N. Cui, and J. M. Guerrero, "A cell-to-cell battery equalizer with zero-current switching and zero-voltage gap based on quasi-resonant LC converter and boost converter," *IEEE Trans. Power Electron.*, vol. 30, no. 7, pp. 3731–3747, Jul. 2015.

- [31] K. M. Lee, Y. C. Chung, C. H. Sung, and B. Kang, "Active Cell Balancing of Li-Ion Batteries Using LC Series Resonant Circuit," *IEEE Trans. Ind. Electron.*, vol. 62, no. 9, pp. 5491–5501, Sep. 2015.

- [32] K.M. Lee, S.W. Lee, Y.G. Choi, and B. Kang, "Active balancing of Liion battery cells using transformer as energy carrier," *IEEE Trans. Ind. Electron.*, vol. 64, no. 2. pp. 1251–1257, Feb. 2017.

- [33] S.W. Lee, K.M. Lee, Y.G. Choi, and B. Kang, "Modularized design of active charge equalizer for Li-ion battery pack," *IEEE Trans. Power Electron.*, vol. 65, no. 11, pp. 8697–8706, Nov. 2018.

- [34] Y. Shang, Q. Zhang, N. Cui, B. Duan, Z. Zhou, and C. Zhang, "Multi-cell-to-multi-cell equalizers based on matrix and half-bridge LC converters for series-connected battery strings," *IEEE J. Emerging and Selected Topics in Power Electron.*, to be published.

- [35] Ye Li and Yehui Han, "A Module-integrated distributed battery energy storage and management system," *IEEE Trans. Power Electron.*, vol. 31, no. 12, pp. 8260–8270, Dec. 2016.

- [36] W. Huang and J.A.A. Qahouq, "Energy sharing control scheme for state-of-charge balancing of distributed battery energy storage system," *IEEE Trans. Ind. Appl.*, vol. 62, no. 5, pp. 2764–2776, May 2015.

- [37] J. Qi and D.D.C. Lu, "A preventive approach for solving battery imbalance issue by using a bidirectional multiple-input Cuk converter working in DCVM," *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 7780–7789, Oct. 2017.

- [38] D.F. Frost and D.A. Howey, "Completely decentralized active balancing battery management system," *IEEE Trans. Power Electron.*, vol. 33, no. 1, pp. 729–738, Jan. 2018.

- [39] H. Chen, L. Zhang, and Y. Han, "System-theoretic analysis of a class of battery equalization systems: mathematical modeling and performance evaluation," *IEEE Trans. Veh. Technol*, vol. 64, no. 4, pp. 1445–1457, Apr. 2015.

- [40] B. Dong, Y. Li, and Y. Han, "Parallel architecture for battery charge equalization," *IEEE Trans. Power Electron.*, vol. 30, no. 9, pp. 4906– 4913. Sep. 2015.

- [41] Z. Zhang, H. Gui, D.J. Gu, Y. Yang, and X. Ren, "A hierarchical active balancing architecture for lithium-ion batteries," *IEEE Trans. Power Electron.*, vol. 32, no. 4, pp. 2757–2768, Apr. 2017.

- [42] C. Hua and Y. H. Fang, "A charge equalizer with a combination of APWM and PFM control based on a modified half-bridge converter," *IEEE Trans. Ind. Electron.*, vol. 31, no. 4, pp. 2970–1979, Apr. 2016.

- [43] Y. Shang, B. Xia, C. Zhang, N. Cui, J. Yang, and C.C. Mi, "An automatic equalizer based on forward-flyback converter for series-connected battery strings," *IEEE Trans. Ind. Electron.*, vol. 64, no. 7, pp. 5380–5391, Jul. 2017

- [44] C. Zhang, Y. Shang, Z. Li, and N. Cui, "An interleaved equalization architecture with self-learning fuzzy logic control for series-connected

#### IEEE POWER ELECTRONICS REGULAR PAPER/LETTER/CORRESPONDENCE

- battery strings," *IEEE Trans. Veh. Technol.*, vol.66, no. 12, pp. 10923–10934, Dec. 2017.

- [45] Y. Shang, N. Cui, B. Duan, and C. Zhang, "A global modular equalizer based on forward conversion for series-connected battery strings," *IEEE J. Emerging and Selected Topics in Power Electron.*, vol. 6, no. 3, pp. 1456–1469, Sep. 2018.

- [46] T.M. Bui, C.H. Kim, K.H. Kim, and S.B. Rhee, "A modular cell balancer based on multi-winding transformer and switched-capacitor circuits for a series-connected battery string in electric vehicles," *Applied Science*, vol. 8, no. 8, pp. 1–21, Aug. 2018.

- [47] M. Uno, K. Yashiro, and K. Hasegawa, "Modularized equalization architecture with voltage multiplier-based cell equalizer and switchless switched capacitor converter-based module equalizer for series-connected electric double-layer capacitors," *IEEE Trans. Power Electron.*, vol. 34, no. 7, pp. 6356–6368, Jul. 2019.

- [48] M. Uno and K. Hasegawa, "Simple modular equalization system with reduced switch count and constant current characteristics for seriesconnected EDLC modules," in Proc. Int. Conf. Power Electron., ECCE-Asia, pp. 1440–1447, May. 2019.

- [49] K. Sano and H. Fujita, "Performance of a high-efficiency switched-capacitor-based resonant converter with phase-shift control," *IEEE Trans. Power Electron.*, vol. 26, no. 2, pp. 344–354, Feb. 2011.

- [50] EATON (2019, Dec.) Supercapacitors. [Online]. available https://www.eaton.com/us/en-us/products/electroniccomponents/supercapacitors.html

- [51] Maxwell (2019, Dec.) Ultracapacitor Modules. [Online]. available: https://www.maxwell.com/products/ultracapacitors/modules

- [52] J. W. Kimball, B.T. Kuhn, and P.T. Krein, "Increased performance of battery packs by active equalization," in Proc. IEEE Veh. Power Propulsion Conf., pp. 323–327, Sep. 2007.

- [53] S. West and P.T. Krein, "Equalization of valve-regulated lead-acid batteries: Issues and life test results," in Proc. Int. Telecommun. Energy Conf., pp. 439–446, Sep. 2000.

- [54] D. Andrea, Battery Management Systems for Large Lithium-Ion Battery Packs, Boston: Artech House, 2010, ch.3.2.3.3.

- [55] M. Zolot, A.A. Pesaran, and M. Mihalic, "Thermal evaluation of Toyota Prius battery pack," SAE Trans., 2002-01-1962, Jun. 2002.

- [56] Y. Chung and M.S. Kim, "Thermal analysis and pack level design of battery thermal management system with liquid cooling for electric vehicles," *Energy Conversion and Management*, vol. 196, pp. 105–116, Sep. 2019.

Masatoshi Uno (M'06) was born in Japan in 1979. He received the B.E. degree in electronics engineering and the M.E. degree in electrical engineering from Doshisha University, Kyoto, Japan, and the Ph.D. degree in space and astronautical science from the Graduate University for Advanced Studies, Hayama, Japan, in 2002, 2004, and 2012, respectively.

In 2004, he joined the Japan Aerospace Exploration Agency, Sagamihara, Japan, where he

developed spacecraft power systems including battery, photovoltaic, and fuel cell systems. In 2014, he joined the Department of Electrical and Electronics Engineering, Ibaraki University, Ibaraki, Japan, where he is currently an Associate Professor of Electrical Engineering.

His research interests include switching power converters for renewable energy systems, life evaluation for EDLCs and lithium-ion batteries, and development of spacecraft power systems. Dr. Uno received the Isao Takahashi Power Electronics Award in 2018.

**Koki Hasegawa** was born in Japan in 1995. He received the B.E. degree and M.E degree in electrical engineering from Ibaraki University, Ibaraki, Japan, in 2017 and 2019, respectively.

Since 2019, he has been with Seiko Epson corporation. His research interests include cell voltage equalizers for EDLCs.